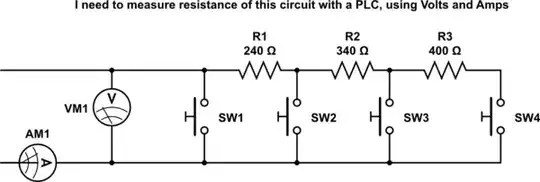

I have a fully differential instrumentation amplifier circuit with a gain of 536 to map a 3mVpp signal (centred around 1.65V) to +/-1.6V, as shown here.

My signal bandwidth is 250Hz, and I would like to use a 12bit differential ADC (stm32g491) with oversampling (128kHz<fs<5MHz) to get as high ENOB as possible. My noise sources are digital noise from the surrounding system (not too close) plus noise from the circuit's components.

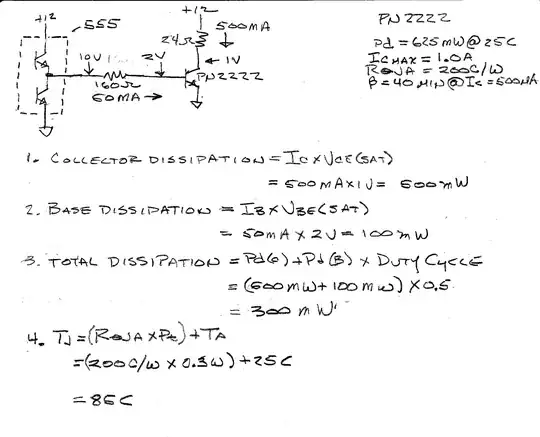

I've done the noise analysis in LTSpice for the 5MHz frequency range I could potentially be looking at:

I furthermore simulated the THD for a 200Hz signal:

All of these simulations seem feasible, and I feel like I have all the information needed, yet I cannot find out how to calculate the ENOB of my system. None of the equations I tried gave me sensible number (therefore I was using them wrong...). I've seen vague suggestions to use MATLAB to get these measures, but I'm unsure what data I should export - would the FFT plot be sufficient?

My THD is calculated for a specific frequency, and it feels weird that the ENOB would be dependent on this value. What about the noise floor in the FFT plot? I am furthermore uncertain how to bring in the noise plot to this calculation: should I limit the noise plot to 0-250Hz and take the RMS value (203uV) and add the square of this to the harmonics to get THD+N? But then how does oversampling + digital filtering help with noise reduction?

Anyone who could shed some light on this problem I'm facing would be greatly appreciated.

EDIT 1

Based on the comments/answers below and some extra research, I may have a solution.

Given that my digital filter's stopband is at 250Hz, the SNR of the differential analogue stage over the 250Hz BW can be calculated as follows: \$SNR_{preamp} = 20*\log(2*V_{RMSsig}/V_{RMSnoise})=20*log(2.26/203u)\approx81dB\$ Which means that the circuit has effective bit resolution of

\$\dfrac{SNR_{preamp}-1.76}{6.02}\approx13.1 bit\$

This implies that even if the differential ADC's ENOB is higher than this value, I wont be able to extract more than 13.1bit information, even with oversampling.

However, if somehow I managed to increase the \$SNR_{preamp}\$ to >16bits, I could use the STM32G4's 12bit ADC (ENOB 10.9bit in differential mode) at, say, 2.5MHz to increase the ENOB of the ADC to >16bits.

This is based on the assumption that oversampling only reduces the quantization noise and has no effect on the preamp's noise.

Could someone check if my thought process is correct here?

EDIT 2

Notice that since the ADC is fully differential it sees, \$V_{RMSsig}-(-V_{RMSsig})=2*V_{RMSsig}\$ at its inputs. The doubling of the RMS value effectively adds a bit to the effective resolution.