I'm tasked with making a 4-7 decoder for a 7-segment LED (common anode).

You can also implement the logic table with multiplexers directly: set their inputs with the desired output values. This is definitely simpler and often faster, too, than and-or gates. Especially for early CMOS logic (mid-late 70s): the 8-1 mux propagates in about the same time as a 4-input gate (say CD4512).

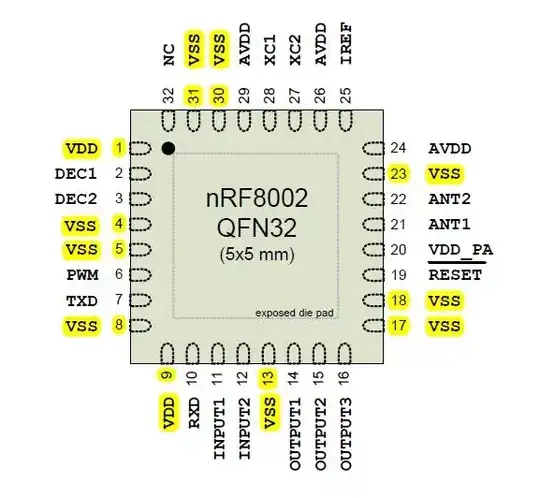

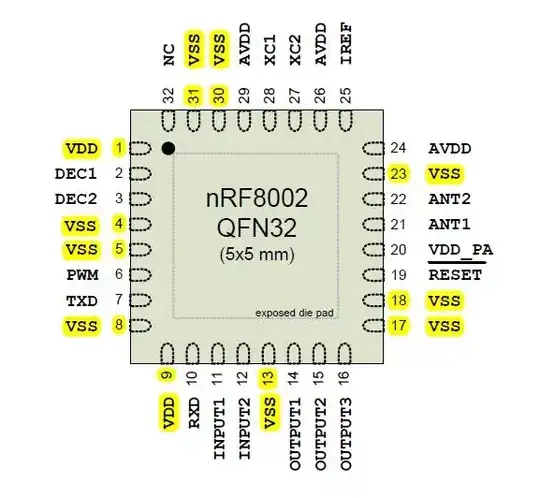

For example:

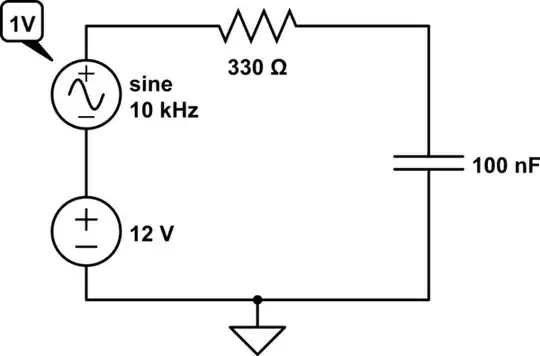

simulate this circuit – Schematic created using CircuitLab

We of course don't need two multiplexers: one will do.

simulate this circuit

So, a 7-segment decoder with multiplexers is essentially 7xCD4512 + 1xCD4069, or their 74xx equivalents.

That's how modern logic is implemented anyway: the LUTs inside of FPGAs, for example. It is somewhat awkward that we often start with a truth table, translate it into equations in VHDL or Verilog, and that gets translated back into a truth table that's then provided as an input to a MUX. For wide-output LUTs, several parallel MUXes share a decoder/driver section to minimize die area.

On a digital ASIC, it's not unusual to have all combinatorial functions use LUT cells (fixed-input MUXes). Any n-input function is the same layout, with different metallization to select 1s and 0s going to the inputs.

Putting combinatorial logic together out of actual gates is mostly a retro-electronics and retrocomputing adventure at this point. Even if you're doing discrete stuff, for anything that can't be solved with one or two gates, or a matching combinatorial function (decoders, for example), a LUT wins every time. And that applied even in the 70s - a lot of glue combinatorial logic could have used MUXes instead. And it's not a recent discovery, of course: this approach was widely taught, and was publicized in popular design books, such as those by Don Lancaster (TTL Cookbook, CMOS Cookbok published in mid-70s!).

There is a certain tendency to teach slightly useless concepts in engineering, and Karnaugh maps aren't very useful whether you design discrete logic or VLSI...