I am designing an SMD PCB to control two motors that consume 6 amperes each. I have too many components and I am using 4 layers, but it is very disorganized, so I want to separate the tracks.

I want to know how to separate those tracks, and in which layers can I put the signals power, the signals control and the differents signals in the board.

I have found information about the power signals must be in a internal layer but the power signals in my circuit need a wide track (5 mm) so I put it in an external layer, is that ok? Do I need a ground plane or power plane?

My circuits specs are: One ESP32 for control the H bridges of the motors

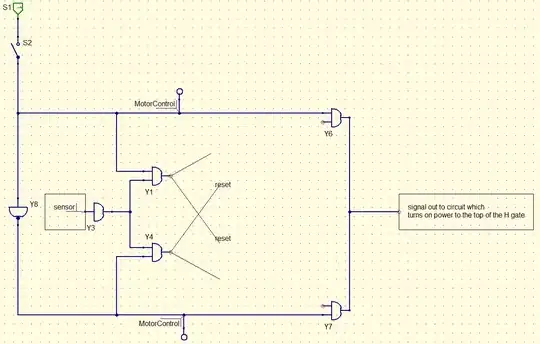

- Two H bridge with N-channel MOSFETs

- Two current sensors

- Two ADC converters

- Two voltage regulators (3.3V,5V)

- Four weight sensors

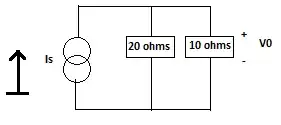

The connection of signals power in my circuit: