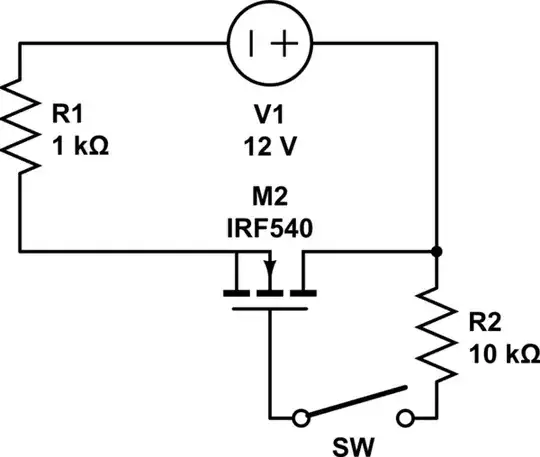

I'm trying to make a voltage controlled amplifier circuit to control the feedback level of a delay effect. My big problem is that the circuit must be powered by a single power supply. I seem to have managed to put together a stable circuit from various sources, but I have a few questions:

- The output level is slightly shifted: -257 / 245 mV instead of -245 / 245 mV. This is fine? Why is this happening and should I fix it somehow?

- Are there any other serious errors in the circuit that I should look out for?

- CV input on schematic is disconnected on purpose. When connected it works fine - the signal level varies depending on the triangular wave from 0 to 100%.