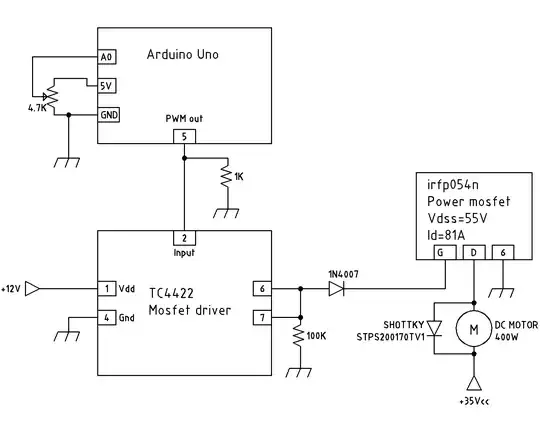

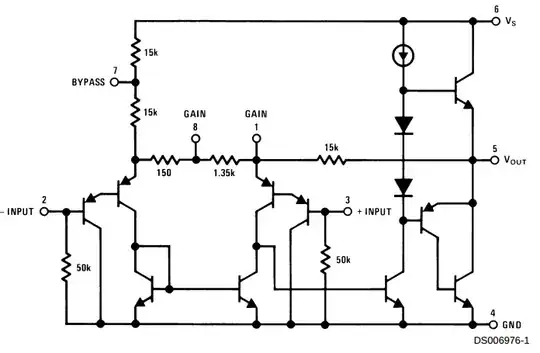

My boost converter boosted voltage for a few seconds but it made a crackling sound, probably burnt. It doesn't switch the MOSFET now and TL494 is getting hot from the upper side which is where error amplifier pins are placed. The schematic is below:

I didn't have any input resistors for TL494 error amplifiers and I would like to know if they are relevant. Because in every application I see on the internet, even in the TL494 datasheet there is some resistor between the ref pin and error amplifier pin.

By the way, I had to invert the pin of the second error amplifier grounded beforehand which actually is a bad idea because even though the error must be zero in the ideal case, it was overwriting the feedback. Basically FB pin was always 4.8 V no matter what is applied form PIN1. By connecting PIN15 to ref pin as in the schematic, I managed to solve that issue until the crackling sound, now FB pin is fixed to 4.8 V again even though PIN1 is lower than PIN2.

I also made a test where I pulled FB pin to ground with an external wire to test MOSFET, which worked but this might have damaged the error amplifier. I want to replace the TL494 with a new one but I must be sure that input resistors aren't necessary. Otherwise, it will be extra work to create paths for resistors between REF-PIN2, REF-PIN15, PIN16-GND on an already printed PCB.

Thanks.

Edit:

Specs:

- Vi: 7V-18V

- Vo: 14V-100V

- Max Ii: 10A

- Max Io: 8A

- Max Power: 120W

I added the resistors for OpAmp inputs as below:

Edit 2:

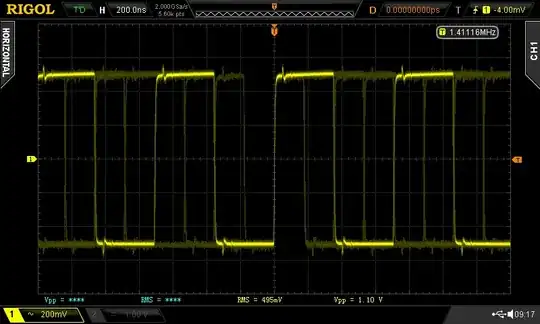

It wooooorks, I replaced TL494 with a new one. I'll halve the inductance because they have 0.2ohm DC resistance and it creates loss at high current. Inductor current ripple will be %35 at most I think this is feasible.