Your and @Simon_Richter's comments are key here, on principles at least. The amount is all that's the matter.

To clarify the relevant amounts, then:

The fundamental wavelength is unimportant; edge rates matter.

The electrical length of the rising edge, even from a fast MCU of ~1ns (~20cm), is relevant to signal quality purposes. It is still insignificant over this length (7cm, assuming a straight-line route).

The short length, means the trace can be modeled as a simple L, C, LC or R element; which one, depends on its impedance relative to its termination(s).

In this case, due to dielectric thickness and available trace widths, and the high impedance load (assuming it's a CMOS input pin), it seems likely the trace will have a lowish impedance, so it will manifest as C.

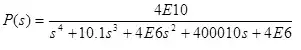

You have the option of using a minimum source impedance equal to the CMOS pin driver impedance (typically ballpark 40-70Ω), or higher (by adding external source termination). A higher resistance gives an effective R-C low-pass circuit. You could also use series inductance to make a 2nd order low-pass, or in general, any filter network between driving pin and trace.

If slower edges are tolerable, the lowpass effect can be valuable to reduce harmonics. How far, depends on the acceptable rise time. There should be a maximum risetime specified on the device. (This spec also likely restricts the device from using a sinusoidal input, by the way.)

You may not need the EMI shield, particularly if the harmonics are reduced with excess source termination. The signal can also be filtered explicitly (with an RLC filter section), to attenuate harmonics even faster. It seems unlikely this would be necessary.

Note that the same logic applies to the PDM returned from the device: it should be source terminated or filtered to about the same degree as the clock. PDM has few edges/sec. than the clock driving it, so it will be less critical with respect to RFI (by ~6dB).

As for harmonic content, 250MHz may be -34dB from the 4.8MHz fundamental, but that's still ~50mV peak, and EMI limits are closer to single digit mV. Now, this trace, and the flex extension itself, will behave as an electrically-short antenna, so will have less than unity gain (in the sense of V input → V/m field strength, ignoring antenna factor and other considerations for sake of simplicity). Gain is further reduced by the wide ground and poor coupling off a microstrip trace. It may be that no additional filtering is required, that the antenna gain is less than -34dB to begin with; if it turns out it's higher than this, then somewhere between 0 and 34dB of filter attenuation would be in the right ballpark to deal with it. This could require a high order LC filter to achieve such attenuation, while still respecting risetime requirements; most likely the shield would be preferable at that point.

Most likely, other elements in the circuit will be more prone to EMI, particularly any connectors, or any sections operating on higher voltages and currents (e.g. switching regulators).