I'm trying to build a frequency counter with a resolution of 1 Hz that will count any frequency between 0 and 999 Hz and hold that value. I've built the following in Multisim but I'm having trouble getting it to work.

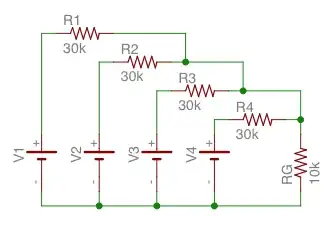

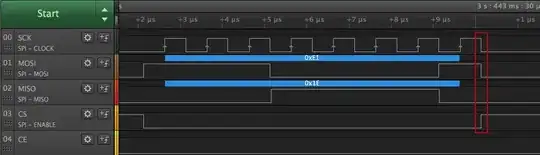

The block diagram is the part inside the red perimeter...

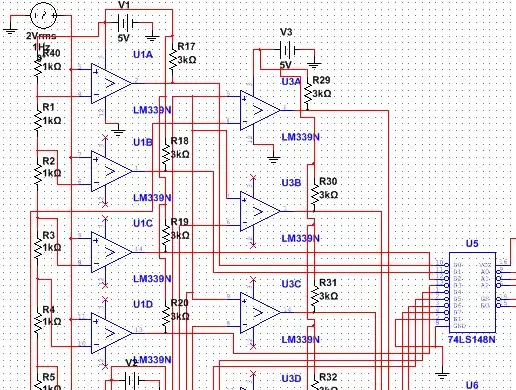

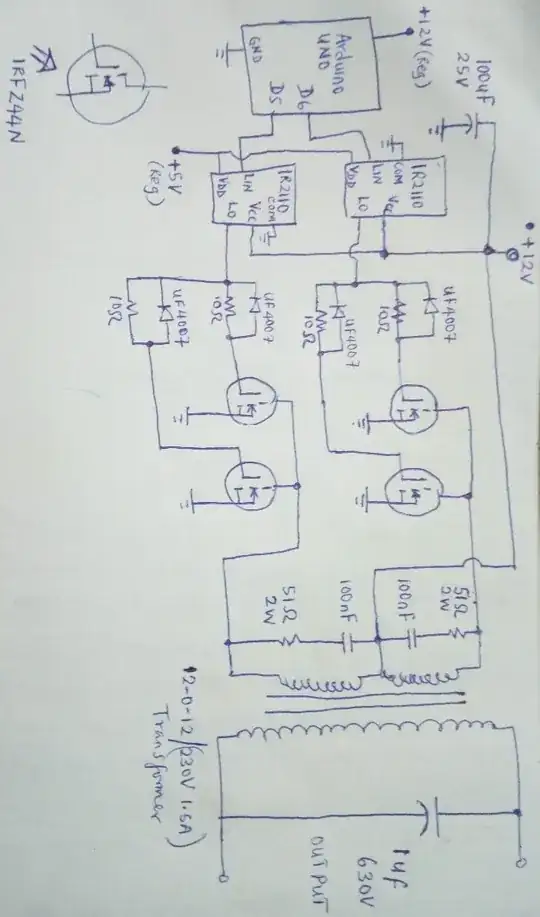

Circuit in Multisim...

Here the frequency I want to display is the 120Hz signal. However, it only counts rather than directly displaying the 120Hz frequency and I've been able to get it to display up to 112 in Multisim after letting the simulation run for about an hour.

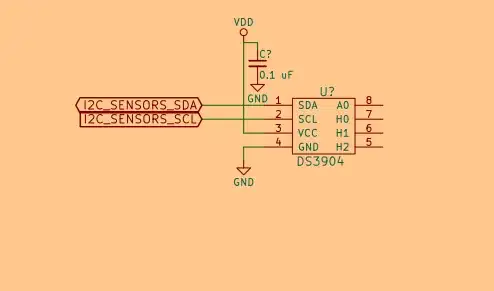

Also there is a bug in Multisim that prevents the crystal from working properly, which is why the digital clock is used to produce the 32.768kHz signal as show here:

UPDATE:

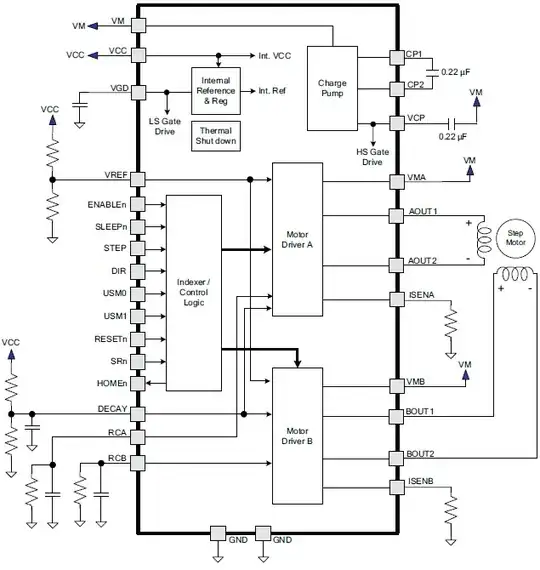

I was able to get it to count to 234 and then reset to 000 with the following:

Can someone please tell me how to get it to hold the final count value?