I'm using HyperLynx to emulate my STM32MP157AAA3 small form factor system board with DDR3-1066 memory.

When I use DDRx batch simulation:

- I confirmed that my ODT model is configured correctly. Use 48 ohm Z0 and 120 ohm ODT resistors.

- I found that all the simulations passed except DQ reading simulation.

- I found that the DDRx emulation data embedded in Hyperlynx requires that the data must be at least 225ps slower than the clock line (for example, DQ is slower than DQS, DQS is slower than CLK, and CA is slower than CLK). But the ST manual doesn't require DQ to be slower than DQS.

- I found that during DQ reading simulation, the setup time of the data line is only about 250ps. But for the same data line, during DQ writing simulation, the setup time is higher than 550ps.

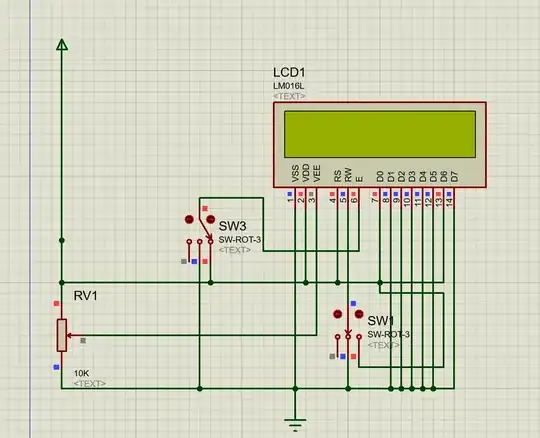

- I found that BadSignal is reported during DQ reading simulation, at this time the oscilloscope shows two thresholds "Setup_high" and "Setup_low". The DQ line crossed Setup_high due to ringing, but did not cross Setup_low.

The question I want to ask is:

- Do you need to strictly follow DQ is slower than DQS, DQS is slower than CLK, CA is slower than CLK" or just adhere to the requirements of the ST manual

- Why is the signal of the same trace seriously degraded during reading and good during writing? Is it a problem of equal length mismatch/impedance mismatch?

- In theory, as long as the level is not lower than Setup_low, the memory should be able to identify the establishment of the signal, why HyperLynx still reports BadSignal.

e.g.

DQ0 on reading got a 250ps setup time

but 500ps+ on writing

it got no overshoot or undershoot in transient simulation

even nice eye pattern

also the two picture on the left are BAD_SIGNAL, on the right are "GOOD".I can't find any difference between them