I am building a 3.3V -> 15V/100mA boost converter using MC34063. I have used formulas in the datasheet to calculate values of components. Then I spotted some oscillations in Vout and instability of inductor current. Is this normal behaviour of MC34063? It looks to me like an unstable operation, but IC doesn't have a comp pin for compensation.An additional question is about DRC input. How to properly estimate the value of the R2 resistor. When I put in 180 ohms (DS value) nothing seems to work. Fsw approx 50 kHz

-

1I'm not sure I trust LTspice to accurately model voltage changes that small. What happens when you reduce the maximum time step? – Spehro Pefhany Nov 12 '22 at 18:31

-

1...or add `.opt plotwinsize=0` (to disable waveform compression). Alternately, the model may have its quirks. There is a model from the late analogspiceman in the [LTspice group](https://groups.io/g/LTspice/), in fact, right now there's a [thread](https://groups.io/g/LTspice/topic/mc34063_models_experiment/94951300) about it. That's a model you can trust. However, this looks like improper ramp compensation, maybe worth investigating (3.3 to 14 V is not large but not relaxed, either). – a concerned citizen Nov 12 '22 at 19:03

-

Reducing the time step has no effect on waveform I still have these empty spaces. – Vasiliy Nov 12 '22 at 20:27

-

2This signal is, what I expect from a hysteretic "take it or leave it" contol loop. There is no linear error amplifier with PWM. – Jens Nov 13 '22 at 01:06

-

3The MC34063 is a hysteretic converter and is *unstable* in essence. You do not compensate it. The output ripple envelope depends on the circuit time constants. – Verbal Kint Nov 13 '22 at 07:42

3 Answers

I don't know what model you are using but, I am using the one found here (registration needed to avoid spammers). You'll need to make a minor adjustment: add 0 1k to the four arguments of I2 (something to do with a change in the way the PULSE() source now accepts arguments; not everyone agrees with it). You could update your OP with the contents of the .model (don't forget to add ``` at the beginning and at the end of the block of text).

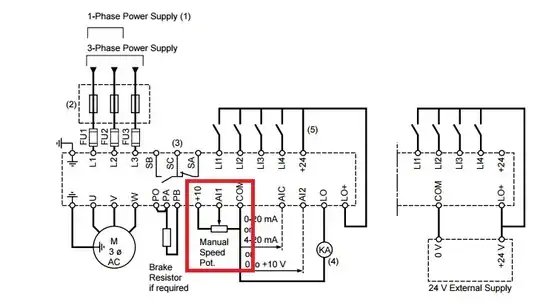

At any rate, I recreated your schematic with the minor adjustment of having the resistor at the DRC pin after the current sense resistor (as seen in the datasheet, p. 13):

The main difference I see is that you have 15 V output, while I see 13.6 V. Maybe it's the model. C2 doesn't influence the output so its value isn't important. D2 might, though, that's why I've chosen one from the database (and added vp to its .model).

However, the ESR of the output capacitors does matter. I don't know what capacitor you've chosen, if it even is chosen from the database but, the lower the ESR the less influence its zero will have on the loop. For example, lowering it to 30m results in this current:

If you intended to "get a feeling" of how the circuit might work prior to building it by using this schematic, you're cheating yourself: never rely on defaults (D1), always add parasitics (Rser). If you want an even better feel then try to add more parasitics, including PCB (e.g. trace inductance, parasitic capacitances). But first, always test the model that it performs as it should. And, not lastly, always take a grain of salt, no matter the results -- not only SPICE is a simulator but, it does so through approximations, sometimes quite gross. For example, this model is behavioural, meaning it tries to model its behaviour, rather than its composition (transistor level), for the sake of speeding up. The price to pay may be deviations from the way the real chip performs.

[edit]

I meat to add this yesterday but forgot (it was too late): if you really need low ESR capacitor at the output then you can add the compensation as a capacitor placed in parallel with R3, like this:

If the ESR is in the single digits (e.g. 1 mΩ) or less then the value of C4 will need to be larger, to lower the zero and bring the phase to a suitable value. If the ESR is large enough then there is no need for C4 (the 1st picture). The difference is that you can get lower output ripple with C4.

- 21,167

- 1

- 20

- 40

-

1I have updated my model and put C out ESR = 50m and it is more stable now. – Vasiliy Nov 13 '22 at 10:38

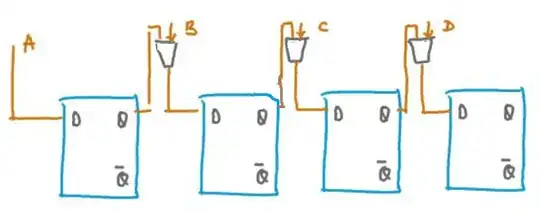

Simulated with microcap v12

Tried also with your R2 = 180 Ohm ... Same behavior, slower.

In some configurations, I have seen also R2 = 0.

Starting waveforms ...

Steady-state waveforms, nothing really strange, within ripple ...

Changed inductor

- 11,004

- 1

- 7

- 20

Regarding the resistor selection on the DRC pin you can take some information from the datasheet for an estimation:

The datasheet mentions in a footnote that the resistor on the emitter follower is 100 Ohm. You will need about 0.7 V across that resistor or 7 mA through it in order to turn on the output BJT Q1. Also a minimum current gain hfe of Q1 of 50 is provided. Finally the saturation Vce of Q2 is given depending on the emitter current of Q1 in a graph.

Intuitively you can see that the 180 Ohms are used at 12 V input and you can guess that at 3.3 V input voltage, the resistor will need to be a lot lower.

We can run some rough numbers: at hfe=50 we need 20 mA base current Ibq1 for 1A output current. We also need 7 mA current through the 100 Ohm resistor. Vce,satq2 will be about 1.5 V. So the resistor should be about:

$$R_{DRC}=\frac{V_{in}-V_{ce,satq2}-0.7 V}{I_{bq1}+7 mA} = \frac{3.3V - 1.5V-0.7V}{20mA+7mA}=41\Omega$$

Checking the calculation with 12V and 180 Ohm results in a significantly higher Ibq1 (>40mA). So you could try a lower resistor than 50 Ohm and see if it makes any difference in the simulation.

- 17,231

- 5

- 37

- 58

- 2,513

- 1

- 8

- 15