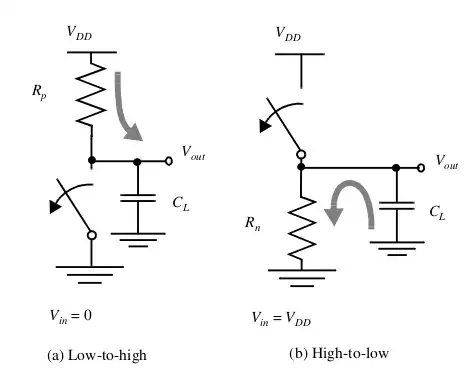

I was reading a book on VLSI design and came across a chapter explaining the working of a CMOS inverter. A part of the chapter describes how the time it takes to switch between high to low or low to high relative to the input voltage is determined by the time constant of an output capacitance that is composed of the capacitances of the connecting wires, diffusion capacitance of the transistors and the input capacitance of the fan-out gates. It was not explained in detail why this was.

Asked

Active

Viewed 25 times

0

-

2Note that for any specific gate voltage, the model replaces the CMOS transistor pair with an equivalent resistance. What's the time constant of an RC circuit? – Ben Voigt Nov 11 '22 at 16:19

-

I was not thinking in terms of how the resistances are placeholders for the effect of varying gate voltage and how the time it takes to switch can be related to the charging/discharging of the capacitor through the two branches, but now that I think about it, it makes total sense. Thanks a lot for your help! – imawful Nov 11 '22 at 20:08