I have a TSX0102 level converter that is powered with local power. I'm running a UART through the TSX0102. The problem is I can't connect a serial to USB converter to the TSX0102 when the board is powered down because it pulls the input high and power bleeds through the TSX0102 inputs (and makes the VCC be somewhere between 0l.3 and 0.6V.)

How do I get a digital buffer to not bleees current through its inputs when the VCC is powered down?

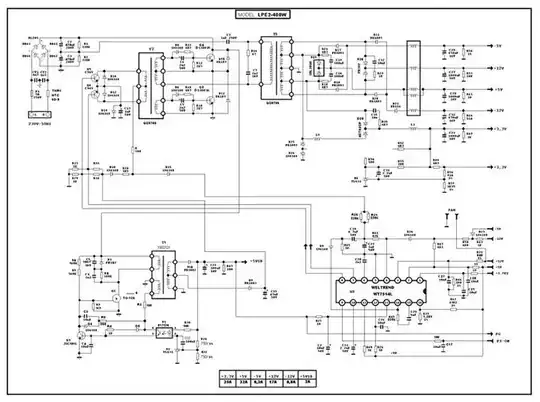

simulate this circuit – Schematic created using CircuitLab