I would like to preface this by saying that my project here is an educational exercise, and I hope that by sharing it and requesting feedback, some other fine folks will learn from it too.

I know that the correct solution here is "use a gate driver IC", but for the sake of argument let's assume we're in the middle of a chip shortage and discrete components are back in style.

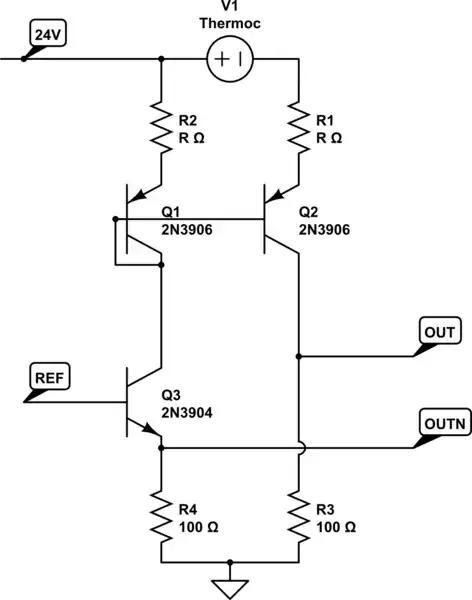

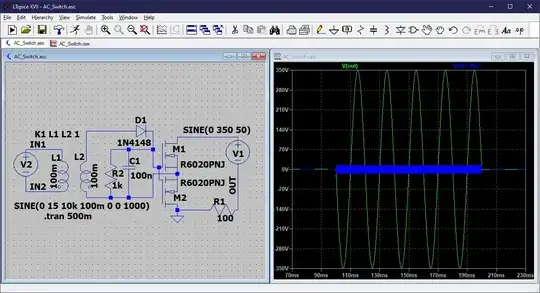

I am making a solid-state relay using NMOS transistors. After much tinkering I can confirm the circuit below works as intended and is able to permit an AC waveform with low impedance, or block it entirely. The AC is between Vpos and Vneg.

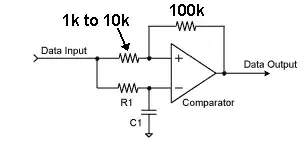

The op-amp at U1 allows me to send a 5 V or 3.3 V signal from a signal source that is not referenced to Vsource1 (like a microcontroller on a switching power supply) which can control the MOSFET. The lower MOSFET Q8's driver has been left as it was when I was simulating, for simplicity.

Now for the question: This works, but I think there is a better way that my inexperience is causing me to miss. All suggestions aside from the obvious "use a gate driver IC" are welcome!

Here's what I've considered:

- I know I could use an optocoupler here, but for the sake of switching speed I chose not to use one.

- A comparator is a better choice than an op-amp for what I've done, but I had the SPICE model for an op-amp handy.

- A Zener diode between the gate and source of each MOSFET would be good to prevent potential Vgs overvoltage, but I have not observed this to be possible: Vboost1 = Vsource1 + 10

Other design notes:

- The BJT totem poles could be replaced with MOSFET equivalents for lower power consumption, faster switching, etc. BJTs are cheaper at the moment, and also their spice models work better in Ngspice.

- Pull-downs R2 and R3 are for safety: when the switch signal is MIA, the MOSFETs are off.

- Vbe does not appear to be exceeded on any of the totem poles. I'm seeing a maximum Vbe of less than 1 V.

All suggestions about how to improve this design are also welcome.

Update:

Curious readers may be interested in an improved schematic. Please note that the design below works in simulation, but is unsafe due to a lack of galvanic isolation between Vsource and the low voltage elements through the charge pump.