I am making a circuit that creates various subdivisions of input frequency by integer values from f/2 down to f/12. Division by 2, 4, 8 are straightforward using JK flip flops. Divisions by 6, 9, 12 can be done via combining divisions by 2 and 3 in sequences. The most tricky are 5, 7, 11.

CD4018 seems to fit the purpose for this task. It's datasheet provides examples of division by 5 and 7 with additional CD4011 on page 5.

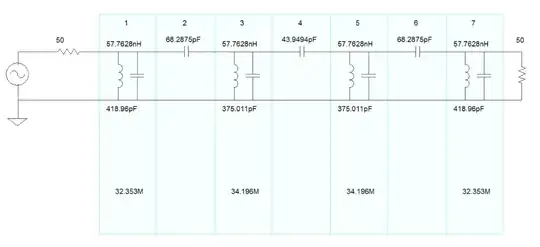

As for division by 11 - according to the datasheet it's possible to use multiple CD4018 to divide by numbers larger than 10. The following appnote provides a circuit for programmable multidecade divider:

I suppose it should be possible to simplify this schematic to the required divide-by-11 but reading its description I am not exactly sure how it works. It seems that "hundreds" can be omitted and J1-J5 on the remaining CD4018s set either to 0 or 1 to provide required value. However I am not sure what to do with additional logic ICs mentioned on the schematic.

I would appreciate if someone could explain how I can accomplish division by 11 using CD4018.