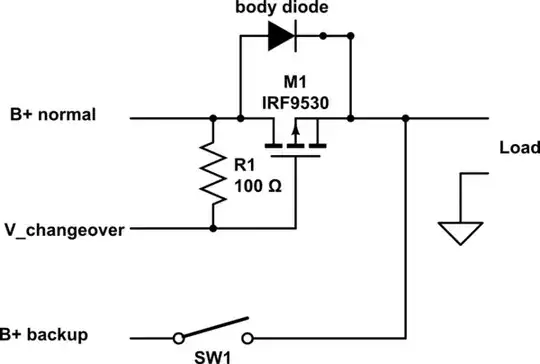

I have the following schematic. This is a NE555 with voltage controlled by a 12 V voltage reference (TL431) providing a PWM of around 10 kHz at a 90 % duty cycle. The PWM then powers the gate of an NMOS (IRFZ44N), allowing current to pass through it.

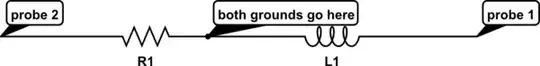

This is my simulated circuit:

This is my simulated results between M1 and R4:

These are my actual results:

My understanding is that NMOSes may have issues with high-speed switching, but if that was the case this should be true for both rising-edge and falling-edge. Also, the listed rise/fall time for my NMOS is 60 ns.

I am unsure what may be causing the attenuation every time the PWM increases. Please let me know if more information is required to solve this issue, I am still relatively new to this.