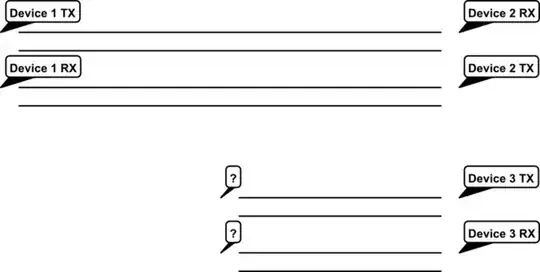

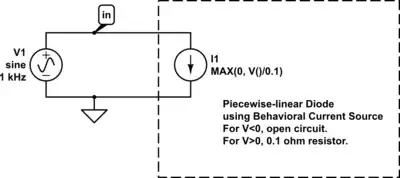

I found this circuit reference online for nRF52810. (Git Source here). The example I used of nRF528210 to make some changes. here

So, the reference Board has this tStrict part:

After doing Copper power, the result of the top and bottom layers is something like this in my system:

The above result shows an error in DRC. I couldn't understand how to fix?

But the PDF example (provided in reference git-source) shows a complete RED patch, it seems completely wrong to me.

Can anyone help me fix the drc error for this?

Edited: Software: EAGLE 9.6.2