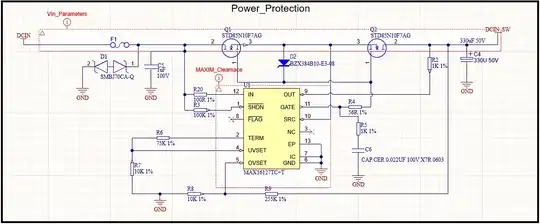

It looks like you've implemented the dV/dt moderation appnote slightly incorrectly with your D1/R4/R5/C6 configuration.

In the appnote, D1 is placed directly between \$V_{SUPPLY}\$ and the IC's gate pin. The 56Ω resistor and 1kΩ/220nF RC arrangement are only connected to the MOSFET gate.

In your circuit, you put the 56Ω resistor in series with both the MOSFET gate and the zener diode.

If you take a look at page 14 of the datasheet, it has this to say about operation beyond 35V:

With proper external component selection, the MAX16126/MAX16127's input voltage operating range can be extended beyond 30V. Normally the input voltage can swing up to 90V in protection mode, but normal operation is listed in the electrical characteristics table to 30V. Higher voltage operation is permissible so long as the resulting GATE bias voltage does not exceed 45V with respect to GND.

To enable operating voltages above 30V, a 6.8V Zener diode clamp can be added GATE-to-SRC to the external switches to limit the maximum GATE voltage. The circuit in Figure 4 shows the recommended arrangement. When VIN = 35V, VGATE = 35V + 6.8V or 41.8V. When VIN > 35V, the MAX16126/MAX16127 detects the input over voltage condition by sensing the voltage at the OVSET pin and turns off the charge pump. The resistive voltage divider on OVSET must be selected to disable the circuit before the gate voltage reaches 45V.

During normal operation the IC uses a charge pump to output a voltage at the GATE pin that is a few volts higher than \$V_{SUPPLY}\$, so that the \$V_{GS}\$ of the MOSFETs remains positive. The charge pump will continually increase its voltage as \$V_{SUPPLY}\$ increases. The maximum voltage allowed at the GATE pin is 45V above GND. The zener diode D1 is used to enforce this - when \$V_{GATE} - V_{SUPPLY} > V_Z\$, D1 starts to conduct and clamps \$V_{GATE}\$ to \$V_{SUPPLY} + V_Z\$.

You selected BZX384B10-G3-08, which is a 10V zener diode. As such you are allowing the GATE pin to reach all the way to 45V, which gives you zero margin. You should use a 6.8V zener diode here, as indicated in the datasheet.

Additionally, because you put the 56Ω resistor in the wrong location, a voltage drop forms across it which is added to \$V_Z\$. This means that the voltage at GATE becomes \$V_{SUPPLY} + V_Z + V_{R4}\$. Since \$V_{SUPPLY} + V_Z\$ is already 45V when \$V_{SUPPLY} \ge 35V\$, this is guaranteed to exceed the allowed maximum of 45V.