I have designed a buck circuit.

The Bode plot of my system is as follows:

I use a type Ⅲ compensator to control my system. The switching frequency is 100 kHz. The cut-off frequency is 20 kHz and the phase margin is 60°.

The transient state of the system does not meet my requirement: when the load is from 100% to 50%, the output can't exceed 12.12 V, but as the plot shows, the max of the output is almost 12.37 V.

I have tried increasing the phase margin (from 60° to 80°) and lower the cut-off frequency (from 20 kHz to 10 kHz) (these methods could improve the damping of the system and reduce overshoot, right?), but the effect is limited. So what else could I do? Could anyone give me some suggestions?

Second Edited:

Thanks to Verbal Kint's book, I have done something to improve the transient response including using two parallel capacitors rather a big capacitor to lower the ESR of the capacitors and increasing the cut-off frequency \$fc\$ (\$fc\$ must be higher than the resonant frequency \$fo\$ of output impedance).Now the \$fc\$ is 30kHz.

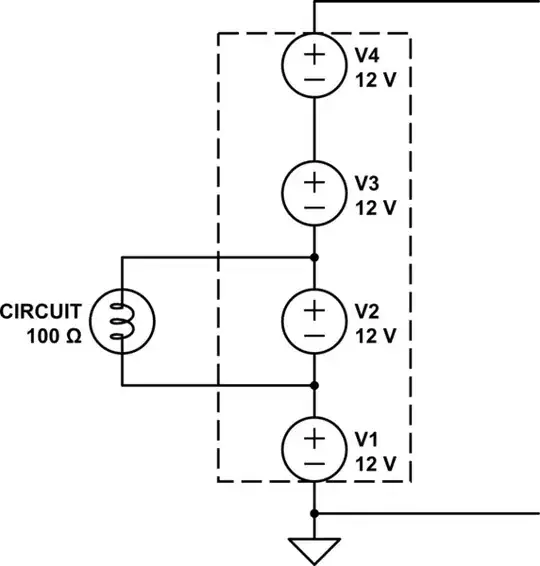

Now The main circuit is as follows:

And now my circuit's transient response is as follows:

when the load is from 50% to 100%, the response is in my expectation: the decrease of Vo is less than 120mV, but when the load is from 100% to 50%, the response still doesn't meet my requirement. I think I can't increase the cut-off frequency \$fc\$ any more, because the nyquist show me that it will become unstable when I increase \$fc\$!! Now what should I do? Thanks for help!