I attempted to design my own H-bridge (P-MOSFET high-side), using a comparator hooked to a one-shot to limit current, modeled after the one-shot current-limited schematic described here.

Upon applying power (VINP is nominally 12 V), the circuit immediately failed. Both low-side MOSFETs failed, observed as less than 1 Ω resistance between all pins in the low-side MOSFETs and ground, whether or not gate current is applied.

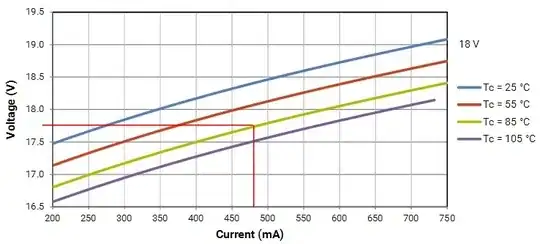

I don't understand the failure. The MOSFETs seemed to fail immediately even before gate charge was applied. I don't think the voltage has ever exceeded 16 V, let alone the rated 20 V.

I'm thinking my next step is to replace the low-side MOSFETs with higher-voltage-rated ones, but it doesn't make sense to me why these failed. Is there some other culprit I'm missing?