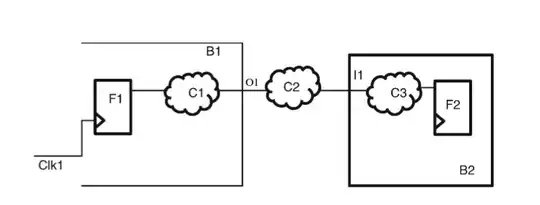

Consider the following circuit in an FPGA:

Let's say the output port O1 is constrained to have a min/max delay of 1 and 3 ns respectively. That means the circuit will be optimized for allowing a max. of 3 ns delay, after the Clk1 trigger, from F1/D to O1.

This will have an impact on the input delay constraint at I1, right? I mean, if the max. output delay at O1 is constrained to 3 ns, and the sum of all the rest of delays until I1 (wires, C2...) is constrained to, say, 10 ns, then the maximum input delay at I1 will need to be constrained to 10+3=13 ns, right?

If this is correct, why do I need to specify the input port delay at I1 if it can be inferred from the max. output delay at O1 and the max. delays from O1 to I1 (wires, C2...)?