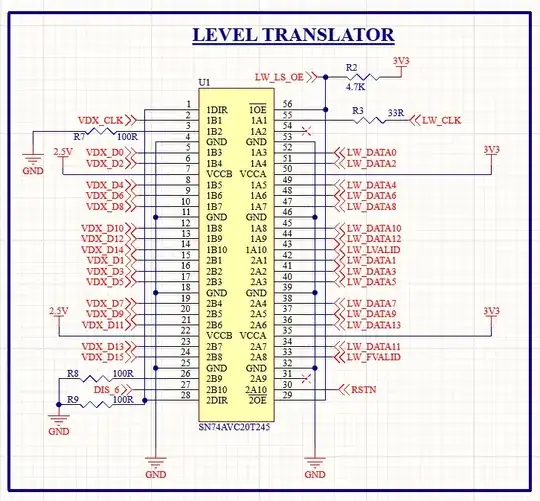

I have a camera core with a DVP interface which has 2.5 V data logic and the system I am using is 3.3 V level. So I have used a TI SN74AVC20T245 level shifter to shift 2.5 V to 3.3 V.

The image from the camera core has a slant noise pattern. I found out the level shifter is injecting noise to GND as the core has an analog ground which is connected to the D GND; it's picking up that noise.

This slant noise is not visible when I remove the level shifter and bypass the data lines.

Has anyone faced this issue? What are all the possible ways to remove the noise with the level shifter?

The clock frequency is 27 MHz.

The board is a 4 layer PCB and has GND on all the layer with stitching vias on all available space. There are no decoupling capacitors and termination resistors on the output side of the level shifter.