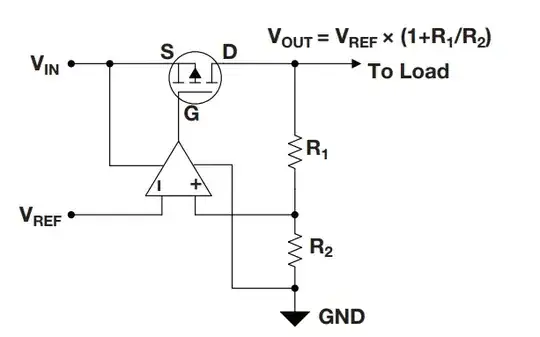

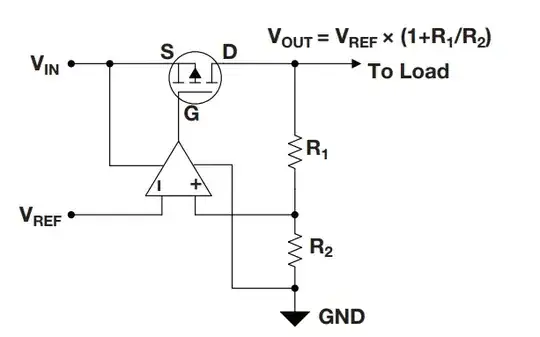

Yes, PSRRs will stack, but... this is a LDO:

(pic source)

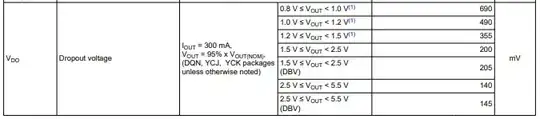

Dropout voltage is the pass MOSFET's Vds. When Vds gets low, the MOSFET's transconductance drops and its capacitance increases, which means it gets slower, the control loop loses both bandwidth and gain, and PSRR drops significantly. When a LDO reaches its specified dropout voltage, the FET is fully on, and PSRR is zero.

Datasheet PSRR is specified for a value of Vin-Vout which is mentioned, and actual PSRR in your application will be lower if Vin-Vout gets close to the minimum dropout voltage. If the manufacturer is honest, they will put PSRR plots with a realistic dropout voltage that corresponds to the most common application.

So there is a compromise, if you don't have much margin between input and output, one LDO may actually have better PSRR that two LDOs in series. But if each LDO has enough Vin-Vout to work, then two in series will offer much better PSRR.