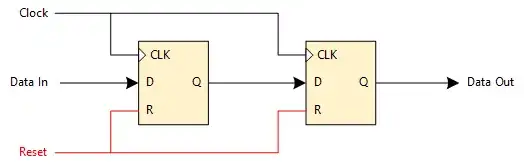

Even if you don't reset 2FF-synchroniser, you can still make it work. When such a 2FF-synchroniser is initially power-on and clocked, it drives an unknown value at its output for 2 clock cycles at most. In the next clock cycle, output will be driven to the actual value as at the valid input. If you make sure that the rest of the design in the clock domain is on reset during this initial clocking period, unknown values will not be sampled by the capturing flop. Once the design comes out of reset, 2FF-synchoronizer would have settled and you would always be sampling the valid input. This could be a scenario in which you may not need a reset in 2FF-synchroniser.

Otherwise in modern FPGAs, 2FF-synchroniser described in RTL may not need a reset, because all the flops have a known value on power-on, which is usually '0' by default. In ASIC, I have seen async clear signal in the 2FF-synchroniser CDC cells to put it in a known state on power-on before even clocking it.

UPDATE:

There could be scenarios where reset is required in 2FF-synchroniser, particularly in ASIC designs. Say for example, consider this case: the design in destination clock domain is reset asynchronously without clock, and released reset. It's clocked later on. First two clock cycles could then propagate an unknown value from 2FF-synchroniser. What if this is '1', and '1' means somekind of trigger to the design (design intent) from the source clock domain, then this is actually a false trigger. But if the synchroniser was reset along with the design, this could have been avoided. So, having a reset in 2FF-synchroniser cell gives the designer flexibility to handle scenarios like this.