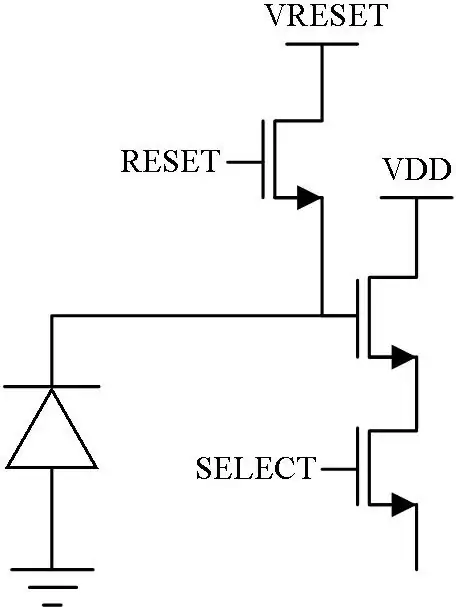

This is a standard pixel circuit: It works just like one would expect. When the reset signal on the gate of the PMOS is low it is conducting and charges the capacitor to 5V, then when the signal turns high it stops conducting and the capacitor is slowly discharged by the current source and its voltage is forwarded to the output by the two NMOSes. This gives an output swing from 4V (since there is a 1V drop across the source follower) down to 0V.

It works just like one would expect. When the reset signal on the gate of the PMOS is low it is conducting and charges the capacitor to 5V, then when the signal turns high it stops conducting and the capacitor is slowly discharged by the current source and its voltage is forwarded to the output by the two NMOSes. This gives an output swing from 4V (since there is a 1V drop across the source follower) down to 0V.

My problem is that the PMOS takes large area on an IC so I would like to replace it with an NMOS as well.

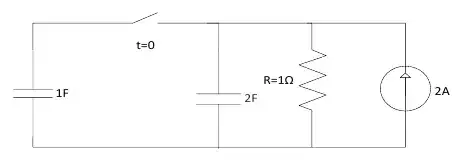

The simplest solution would be just to replace it as it is: However, for some reason the capacitor in this configuration doesn't charge up to 5V only to about 4,2V losing almost a volt on the output range. Can someone explain what is the reason for this?

However, for some reason the capacitor in this configuration doesn't charge up to 5V only to about 4,2V losing almost a volt on the output range. Can someone explain what is the reason for this?

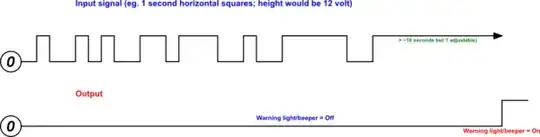

Another solution could be turning the circuit upside down: This seems to work well but I've noticed that the capacitor charges up slower than it discharges in the PMOS circuit giving a slightly different characteristic. I would like to know what is the reason for this difference.

This seems to work well but I've noticed that the capacitor charges up slower than it discharges in the PMOS circuit giving a slightly different characteristic. I would like to know what is the reason for this difference.

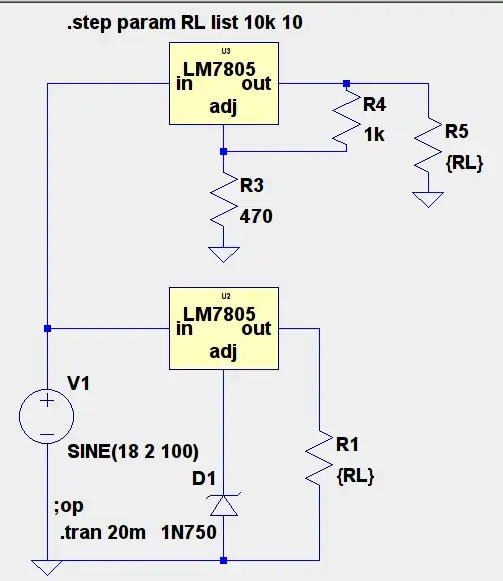

The circuits that appear on the internet seem to be using the first NMOS configuration but with a different drain voltage than Vdd:

Why is this the ideal setup, why is it better than my suggestions, and what would be a suitable voltage for Vreset?