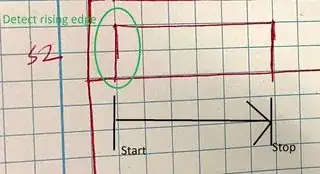

I am exploring ways to shorten the width of the ON-time of a PWM signal while keeping the switching frequency constant. I intend to use S1 as the signal to the Enable/Disable pin of a gate driver IC having such feature and S2 to set the envelope of a PWM stream. My intended application requires a dead time between the falling edges of the last PWM pulse of the pulse stream inside the envelope of S2 and S1. I think delaying S1 using a delay line, then OR gating it with the original signal can produce the elongated signal which I can use as S1. As a reference, I have attached a figure herewith showing two signals (S1, S2), where S2 has reduced ON-time. Is there an IC that I can use to perform this operation?

Asked

Active

Viewed 159 times

0

-

3You need an IC that can predict the future to generate S2. (Alternatively, delay the rising edge, which is easy, but preserve the falling edge). Alternative 2 : use your PWM gen to make S2, and delay its falling edge to make S1. – Aug 08 '22 at 22:37

-

3Is there a reason your PWM controller can't do this? – vir Aug 08 '22 at 22:37

-

1Must guess what's the reason for this? A PWM controller sets the length of the ON-state to 0...100% of the pulse repeating period and it doesn't change the frequency. You want something that you want to keep secret, I guess, and for that reason you ask something else that you think to solve the actual (=secret) problem. - the classic XY-question. But without knowing that actual problem we very easily see your question bizarre. Reveal the actual goal and get better possibilities to get something useful. – Aug 08 '22 at 22:50

-

If the pulses have constant duty cycle to begin with (and constant shorter duty cycle after), then yes: **high-pass filter + comparator** would do that – tobalt Aug 09 '22 at 07:09

-

Something like a CD4098? – Antonio51 Aug 09 '22 at 07:44

-

@user287001, thanks for the comment. I intend to use S1 as the signal to the Enable/Disable pin of a gate driver IC having such feature and S2 to set the envelope of a PWM stream. My intended application requires a dead time between the falling edges of the last PWM pulse of the pulse stream inside the envelope of S2 and S1. I think delaying S1 using a delay line, then OR gating it with the original signal can produce the elongated signal which I can use as S1. Thanks in advance for further suggestion. – Allison Aug 09 '22 at 20:42

-

We still don't know the cause-consequence relations. Is a dumb pulse stretcher OK - a circuit which delays the falling edge of its input pulse (= a pulse which is not drawn in your image) and in that way generates S1? Or should the generator of your drawn S2 somehow guess when S1 somewhere in the future falls and drop S2 a certain amount of time before S1 will be dropped to off state? If the latter, what facts the generator of S2 can use as the basis of the decision when S2 should drop? – Aug 09 '22 at 22:54

-

Do the pulses have a fixed width or duty cycle? – Voltage Spike Aug 11 '22 at 00:14

1 Answers

0

You can detect the rising edge, then do something. You can run a timer or use a delay, you can't do anything with the falling edge, it's not deterministic.

There are many circuits that can do the rising edge detection, I'll leave it to you to design the rest. Hint, once you detect the rising edge, you can run a timer or use a delay or use a filter delay for the stopping point

rising edge (0 to1)and falling edge(1 to 0) detector circuit for flipflops?

Voltage Spike

- 75,799

- 36

- 80

- 208