Say I have a D Flip Flop and I have a resistor, capacitor, diode, and Schmitt buffer to keep its reset line low for a few ms during startup (as per this answer)

This takes care of power-on, but during operation of the circuit if I need to drive reset low, how can I do it? The Schmitt buffer is already driving that pin to a logic high - I suppose one thought is to insert a series resistor between the Schmitt buffer and Reset pin, then drive a low-side FET in order to pull Reset low when desired. Is this the best way to do it, or am I missing some better solution?

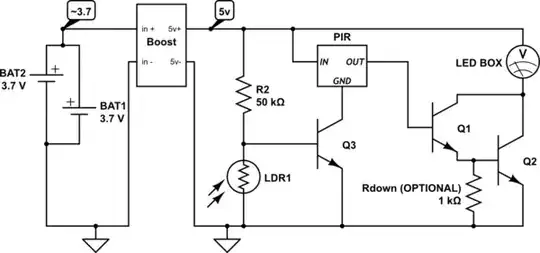

simulate this circuit – Schematic created using CircuitLab

Note: I'm aware the schematic shows an SR latch - the DFF component didn't show a Reset pin and I'm generally unfamiliar with the schematic tool, sorry!