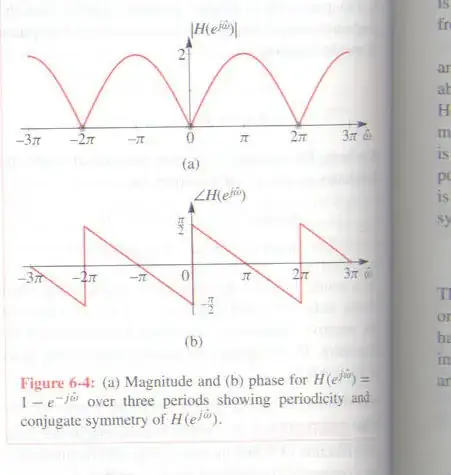

Here the minterms of the SOP representation are ~A~C + AC (XNOR gate). However is there a static 1 hazard between the two terms? When the expression changes from ~A~C to AC, there could be small period where A goes from ~A to A but C has not moved from ~C to C. This would cause an output of 0 for a brief period of time, before the value settles at 1. From the definition this would seem like a Static 1 hazard. However, it doesn't seem like this can be removed with an extra minterm? Does that mean that all static hazards can't be removed with extra terms. Or am I mistaken as to what a static hazard means?

Edit: It seems there is some ambiguity about the definition of a static hazard. The definition I used was this : a static hazard happens when an input transition which should not trigger an output transition makes the output change momentarily, i.e. it generates a single spurious pulse. However it seems there is another way of classifying hazards as in this document. According to this, the XNOR function causes something called a function hazard, and static hazards are for when a single input changes.