I am exploring a tentative design to limit current for charging a VFD bus link capacitor from the AC mains. Simple analog current limiters using resistors and transistors are inefficient and problematic when dealing with peak charging current from a full wave bridge rectifier, as I discovered in answering a similar question recently. So I think this will require a switching regulator design using PWM and an inductor. I simulated a circuit using LTSpice that seems promising, but I see very high power spikes when the MOSFET is turned on and off.

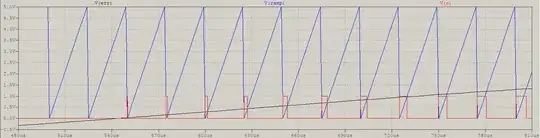

This is to be expected, as the device will transition from a condition with as much as 350 V when OFF, to a peak current of up to 20 A in the inductor, so during switching there may be simultaneously as much as 7000 W. LTSpice shows spikes of several thousand watts, but duration is in the order of 100 ns.

I was able to somewhat reduce the amplitude of these transients by using an RC snubber across the device, and with a gate resistor which reduces the switching speed, but both methods dissipate power. I have also found a lot of variation among various NMOS models. When I calculate the average power over a half wave at 60 Hz, it is about 5 W, which is acceptable. But I am concerned about reliability issues due to the high switching transients. I have designed and built similar switching circuits, and they have worked OK, but I'd like some confirmation that these transients might be ignored.

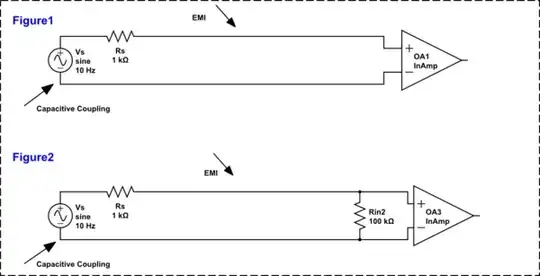

Here is the circuit as it stands. A practical implementation would require a number of refinements, but this is to prove the general principle.

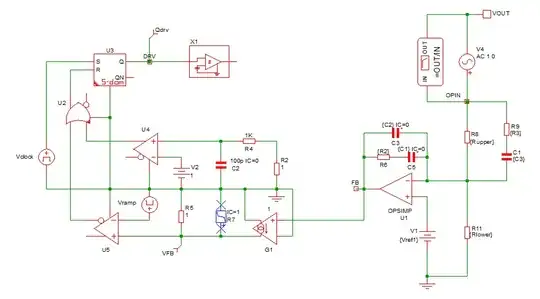

I found that the commutating diode D2 was exhibiting several hundred A of reverse conduction, which caused much of the excessive power spikes noticed. I replaced it with three 150 V Schottky devices and the circuit operation now seems reasonable. Here is the new simulation: