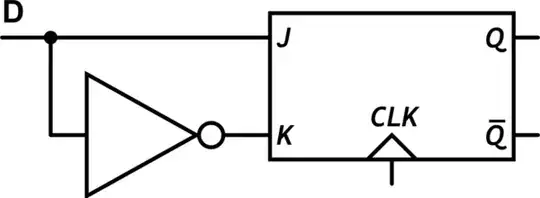

I am currently studying DCDC stability analysis in LtSpice. Could you please check my phase margin calculation, am I right? And how about the gain margin calculation? Is it equal to infinity in my case? This buck converter I checked, works well in transient modeling. To calculate PM I put the AC probe source between the system output and the feedback resistive divider, and after simulation, I created a custom plot of Vout divided by Vin_m (opamp negative input voltage). Is that the correct way to calculate phase margin? According to my calculations, PM = ~22 degrees, and the crossover frequency = ~23 kHz. Bode plot with marker lines

UPD: I changed my schematic according to LvW suggestion, now I am not sure what net I should measure on the bode plot: