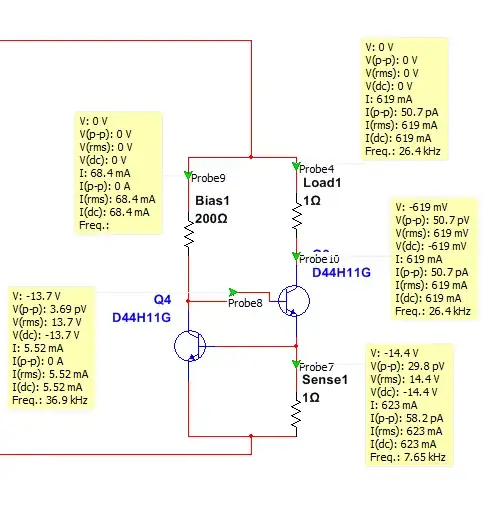

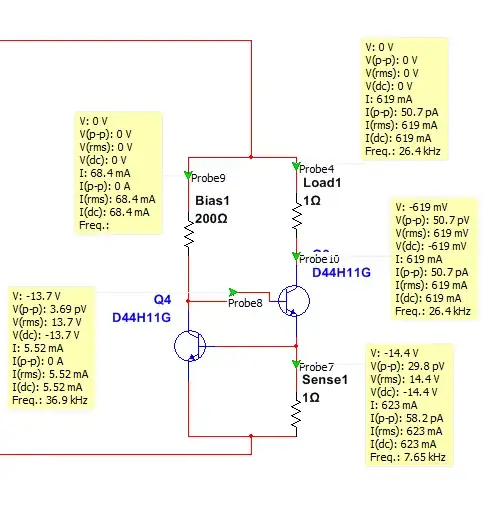

It can be a concern in some cases. It's sometimes worth breaking out components to see. That is, replace each PCB trace and via with its equivalent resistance (or impedance if you're dealing with AC) and simulate. Here's an example:

Imagine you have a 5 inch run that needs to go from the top to the bottom of the board, and you put 4 vias at the 1/2/3/4 inch marks.

4 amps over 1 oz/square foot PCB, 100 mil traces, 5 inches long. Using the default via settings from here for estimated via resistance. One inch of trace here has a little under 5mOhm of resistance. And the vias about 0.75mOhm of resistance.

simulate this circuit – Schematic created using CircuitLab

When you work out the currents through the vias, something funny happens. The first and last vias are taking 1.87 A each, and the two middle vias are only taking 130mA each. (I have the currents set up in the simulation. Run->DC Analysis. I don't know how to show them directly in the answer.)

This is mainly because the vias don't actually have that much resistance overall. It's much higher per unit length, but vias aren't that long. So if you squint a little bit you have two parallel resistors shorted together every so often - and of course you don't have much current flow between the two except at the start and end.

You want the vias close together if possible, or star-connected. Normally this makes no difference. Every once in a while, it does.

(As an aside, trace widths / lengths / etc here are completely made up. Please don't blithely use these numbers.)