For now I'm ignoring the math and the correct terms, and just concentrating on the concepts...

The right sequence

Indeed, circuits (like everything else in life) are best understood in this sequence - first the concepts, then the specific implementations and the details around them. Concepts do not depend on the specific implementations (switches, relays, tubes, diodes, BJT, MOSFET, etc.); they are eternal and immortal - something like the human soul, while the implementations are like the human body.

It is a common mistake to explain the specific circuit implementation and not the basic idea on which it is built. So I will focus on the concepts because disclosing the basic circuit ideas is my favorite activity.

The concepts behind CMOS

Two electrical concepts (electrical analogies) can be used here to explain the basic idea behind CMOS - 3-pole (SPDT) switch and potentiometer. Let's follow the evolution of the CMOS idea..

The problem

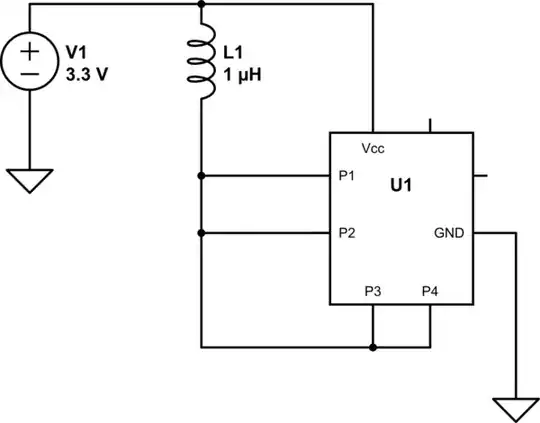

Electrical circuits. Simply put, the output of a digital circuit (logic gate) switches the supply voltage between its two values - Vcc and zero (ground). In household electrical circuits, automotive circuits and in general, this is done by a simple 2-pole switch connected in series between the power supply and the load. Typical examples are car ignition and starter switch.

This configuration works well there because, as a rule, electric loads have low resistance. So when the switch is off, the voltage on the load is zero as it should be.

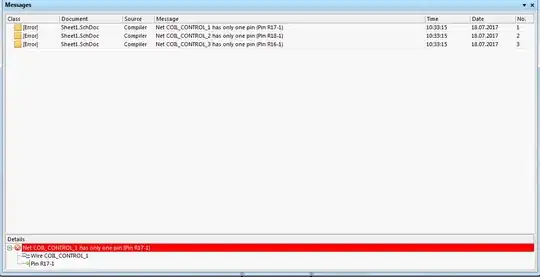

Electronic circuits. Electronic (digital) MOS circuits have high input resistance. So, when cascaded, they act as high-resistance loads. In this case, when the humble 2-pole switch is off (the so-called "open collector" or "open source"), the voltage at the next input will be undefined since it will be affected by various disturbances (e.g. leakegas).

Another problem is the charged input capacitance that cannot find a path to discharge.

There will be a problem also if the load is connected not to ground but to Vcc or to another point having a voltage between zero and Vcc. A typical example are the weird TTL inputs having internal pull-up resistors.

That is why, in these cases, they connect a "pull-down" resistor… but this is not the best solution.

"3-pole (SPDT) switch"

All these problems can be perfectly solved if the digital output acts as a 3-pole switch that switches the output between Vcc and ground.

Transistors are 2-pole switches. Unfortunately, there are no electronic devices with such a 3-terminal output. There are only devices (transistors) whose outputs (collector-emitter, drain-source) act as the humble 2-pole switch. What do we do then?

Composed 3-pole switch. Like in electrical circuits, we can assemble a 3-pole switch by two 2-pole switches with a common pole… and switch them in the opposite direction (never both "on").

CMOS output stage presented as an SPDT switch. So, in the CMOS configuration, a 3-pole composed transistor switch is assembled by two separate transistors acting as 2-pole switches.

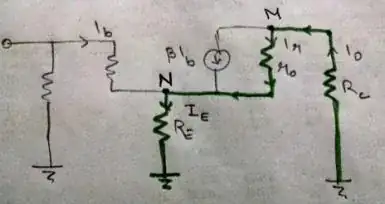

"Potentiometer"

The problem of the SPDT configuration. The 3-pole switch would be a tempting explanation but it has one major drawback - it is not possible to implement :-) The problem is at the time of switching when both unwanted situations are possible - both switches are "on" (short connection) or "off" (undefined output voltage) at the same time.

Potentiometer instead SPDT. That is why, the better explanation of the CMOS output stage is to think of it as a potentiometer where the input voltage "moves" the wiper from the ground to the Vcc rail.

Transistors are 2-terminal variable "resistors". But there are no semiconductor devices acting as 3-terminal potentiometers. There are only devices (transistors) whose outputs (collector-emitter, drain-source) act as the humble 2-terminal variable "resistors" (rheostats). What do we do then?

Composed potentiometer. Like above, we can assemble an "electronic potentiometer" by two "electronic rheostats" with a common point… and control them in the opposite direction. But, in contrast to the "SPDT configuration", here we make it so that they overlap at the time of transition. The two transistors will be "semi on"; so the power supply will be not shorted and the output voltage will not be undefined.

CMOS output stage presented as a

"composed potentiometer". So, in the CMOS configuration, a 3-terminal "composed potentiometer" is assembled by two separate transistors acting as 2-terminal "variable resistors".