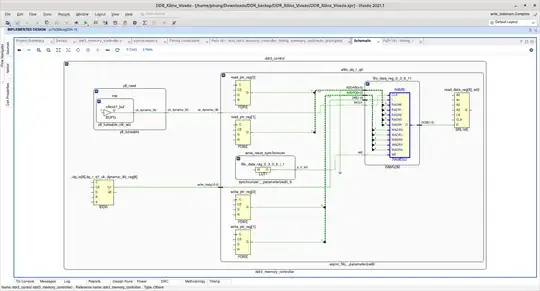

I have implemented an asynchronous FIFO

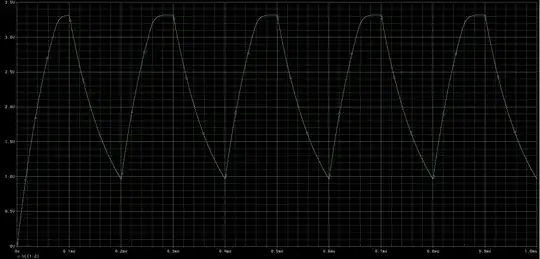

However, I have setup timing violation when read_clk is having phase shift of 270 degrees , and write_clk is having phase shift of 90 degrees.

Both read_clk and write_clk are having the same clock frequency.

Could anyone advise ?

Please see below the reports from Vivado tool: