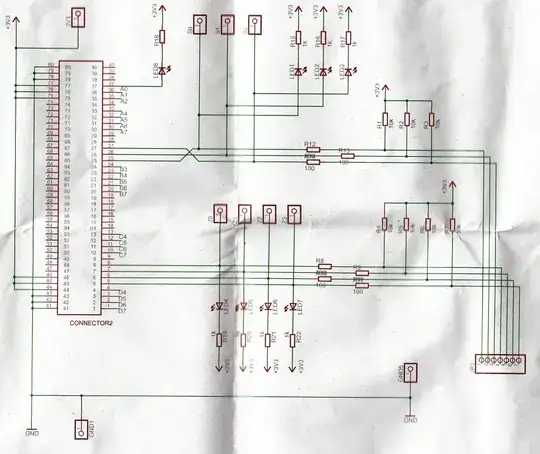

I designed (with help of several online/offline resources) the following current sink circuit with features:

- Should be capable of sinking a maximum of 200 mA (AC, RMS).

- Follows the input sine wave

V1of amplitude359 Vat60 Hzfrequency. - POT

RV1controls the amplitude of the current. - Switch

SW1starts or start/stop the current sink.

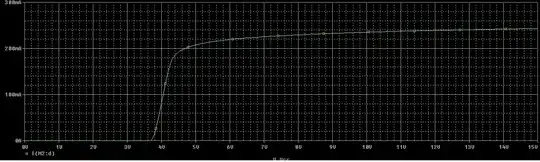

The circuit is working fine as expected. However, when I switch on SW1, an unwanted peak is observed in the current. I suspect that it is because: the base voltage is high at zero current condition. The following figure shows the graph plotted by the oscilloscope. The difference of voltage A and B gives current in mA. The C terminal of the oscilloscope plots the voltage at the MOSFET's gate.

Please suggest to me how I can improve my circuit by eliminating the peak. Also suggest me where else I can improve.

Also note that: Irrespective of initial conditions, the circuit reaches equilibrium with gate voltage high.

EDIT: Simplified Circuit is shown here.

simulate this circuit – Schematic created using CircuitLab

I finally eliminated the SPIKE by adding a 1Mega ohm resitor as shown in the following circuit.