It seemed obvious to me, but then I read all these audio forums where they're talking about overflow, tones, etc. and I just want to make sure I'm not missing something.

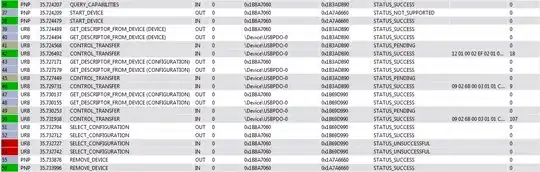

If you take an I2S signal:

and run the serial data (SD) signal through a logic inverter IC (leaving the clocks unchanged), the audio will be flipped and have a tiny DC offset added to it, right? No other consequences? No wraparound distortion or anything?

Serial data is transmitted in two’s complement with the MSB first. The MSB is transmitted first because the transmitter and receiver may have different word lengths.

So for example, if my ADC is outputting 24-bits of audio on a 32-bit word clock, with the remaining bits 0, and the unused channel all zeros:

Then for instance:

- the negative number

0xffffcd00inverts to0x000032ff - the positive number

0x00001600inverts to0xffffe9ff

If the data were 3-bit, the values on the left would just become the values on the right:

| b2 | b1 | b0 | 2C | ~b2 | ~b1 | ~b0 | inv |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | −4 | 0 | 1 | 1 | +3 |

| 1 | 0 | 1 | −3 | 0 | 1 | 0 | +2 |

| 1 | 1 | 0 | −2 | 0 | 0 | 1 | +1 |

| 1 | 1 | 1 | −1 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | −1 |

| 0 | 0 | 1 | +1 | 1 | 1 | 0 | −2 |

| 0 | 1 | 0 | +2 | 1 | 0 | 1 | −3 |

| 0 | 1 | 1 | +3 | 1 | 0 | 0 | −4 |

So it's just an inversion with a small constant DC offset (which doesn't matter for audio), right?

And the unused right channel just becomes 0xffffffff which doesn't matter because 1. that is also just a small DC offset and 2. we're ignoring it anyway, right? (It doesn't bleed into the left channel's bits or anything.)

(Actually, now that I think of it, the better option would be to invert the stereo 24-bit per sample stream, instead of flipping each mono 32-bit per sample stream earlier in the chain. I'm pretty sure that doesn't make any difference and it works fine either way, though.)