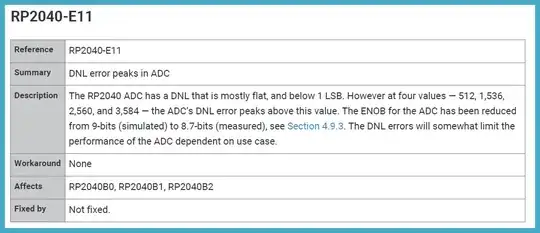

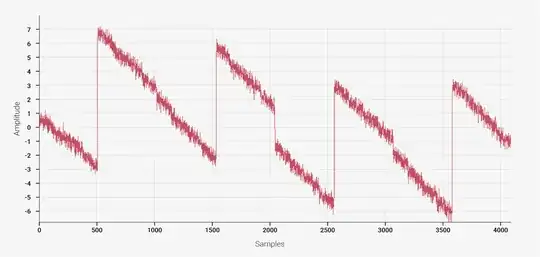

What happens when we reach the values mentioned as "DNL error peaks"?

As you linearly increase the voltage, the digital readout jumps as you reach those DNL error peaks. It can jump in two ways:

- it decreases, in which case you will get the same digital output value for two different input voltage levels,

- it increases, in which case you have missing codes: some digital output values cannot be obtained at all, no matter what the voltage is.

One workaround I've found reliable is to sample the signals twice, the second time with a small offset voltage added, e.g. by turning on a current source that dumps current into the output impedance of the voltage source used. That way, if you determine that the reading is close to one of the DNL peaks, you instead use the other reading, and subtract the offset. The offset can be continuously calibrated: for each pair of readings (one with, one without offset), take their difference and use it to update a digital low pass filter, whose output is then the estimate of the offset you're adding on the analog side of things. The update of this filter is suppressed in the neighborhood of the DNL peak.

Essentially you're losing half the ADC sampling rate if the inputs are within the error bands of the DNL peaks (i.e. within say +/-16 counts of each peak). Otherwise, you can use the offset samples, after offset removal, to reduce the noise level of the signal by averaging both of them.

There are many ways to implement the offset addition of course. Use whatever works without corrupting the signal.