I designed a +/-15V power supply setup and trying to find/fix problems before running another PCB production run.

It will accept 36VDC (800mA) from an off the shelf part via a barrel connector. I cannot change that part of the equation so I'm trying to desing something around that thing.

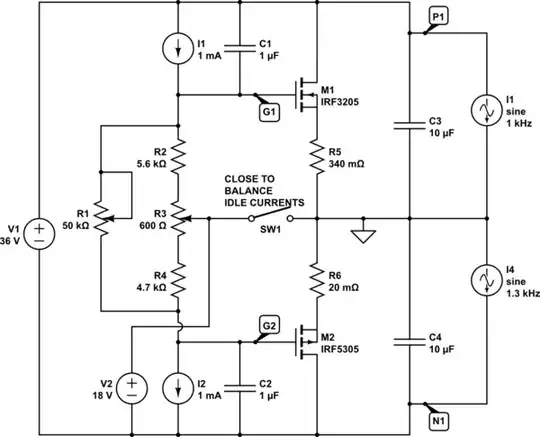

My current layout looks like the following picture:

I plan to use a buffered voltage divider which in turn controls a pair of n-channel and p-channel MOSFET's to provide enough power for the following linear regulators.

I plan to use a buffered voltage divider which in turn controls a pair of n-channel and p-channel MOSFET's to provide enough power for the following linear regulators.

I'm aware of possible oscillations due to the capacitive load on the op amp, I ran some SPICE simulations and found the values in the schematic for sufficient. Here are some screenshots of the measurements with and without the compensation:

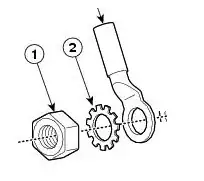

I selected these parts here:

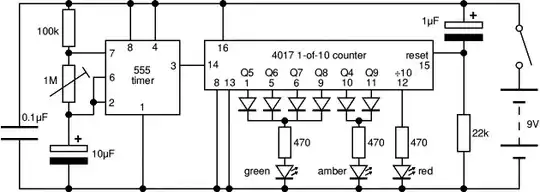

I ran a (quite simple) simulation in circuit.js if anyone wants to follow my train of thought and how I even got here.

My question after this huge preamble is the following:

Am I completely on the wrong path with my idea here or is there a chance of this thing working?

EDIT:

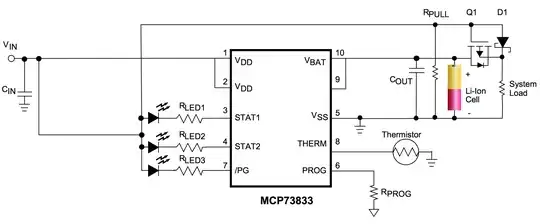

- If there is any large power imbalance in loads, then the driver transistor will dissipate the difference in Watts. i.e. for audio it would be < 50% efficient. If so, the design would be better with differential output driver from single supply.

This answer by Tony Stewart EE75 brought me to the conclusion, that trying to supply power that way isn't feasible in my case and instead I'll go down the road of modifiyng the main circuitry to work with a single-rail supply rather then force that concept of having a positive and negative supply.