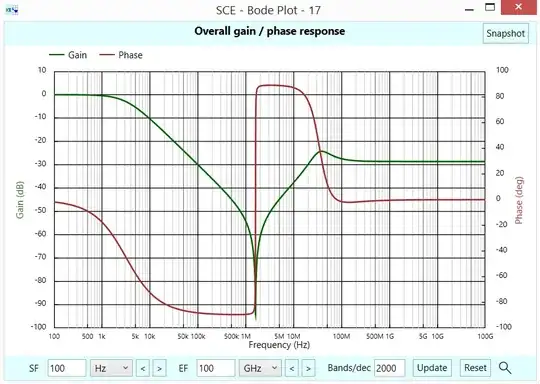

Overshoots and ringing are a sure sign of second order effects.

It may be from +j reactance (L inductance) with -j or C, capacitance or in Active ccts, positive feedback or lack of gain margin in active feedback. (pick 1 or more causes) See my Simulation. On breadboards , it can be due to both L and lack of C near IC.

- We call parasitic R in caps as ESR and inductance as ESL (effective series inductance.)

It may be 2nd order or higher depending on the number of loops in your circuit. Inductance depends on conductor geometry and ln (l/d) in [nH/mm] but tends to vary around 8 nH/ cm +/- x%.

The unexpected part to me was the average V+ was still 3.3V with 33R load.

That tells me the load regulation error was very small like 1% or in other words not a 50R generator of 50 ohms.

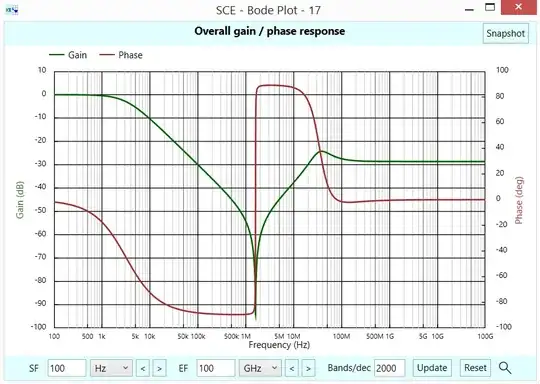

Here is a different version of SIM using JAVA instead of jscript.

general Rules of Thumb

when you match R to source you expect 50% average peak or 99% of Vavg peak with 99x Rsource.

Matching \$\sqrt{L/C}=Zo \$ to source Rs prevents reflections and source of ringing.

But with Transmission line end reflection is more important to match load to Zo and add Rs if necessary to match source but beware of load regulation loss. Conjugate loads means matched R but opposite (-V) reactance to avoid reflections and ringing.

This is why small C shunt helps small L in series.

preventing ringing at source by adding small series R like 22R to logic driving long traces helps with ringing or in your case shunting R with about 100x source R and conjugate inductance.

yet textbook square waveform from an ideal 0 ohm square wave gen requires matched source and load to cable for 50% attenuation or 100x source driver R for decent square response and only 1% loss.

CMOS RdsOn logic tends to be from 10 ohms to 3 kOhms

- it all depends on the Logic family (prefix), voltage and temperature. In the old days it also depended on chip supplier as lithography and shoot thru currents rise with speed and lower Rs cause more ringing.

- Lowest Rs or RdsOn is at coldest T or ARM family with 74LC or 74ALC as Vol typ./Io tends to be around 22 ohms at 3.3V which is also 3.6V max technology due to shoot thru currents.

- then 74 HC is 50 ohm logic at 5V

- then 4000 series is 300 ohm logic at 12V then Rs rises to 3k at lower Vdd.

- ringing occurs when risetime of source is faster than prop. delay of channel or LC latency .

in ACTIVE circuits ringing is a sure sign of stray C positive feedback but mutual coupling of loops or ESL effective series inductance is also a form of crosstalk.

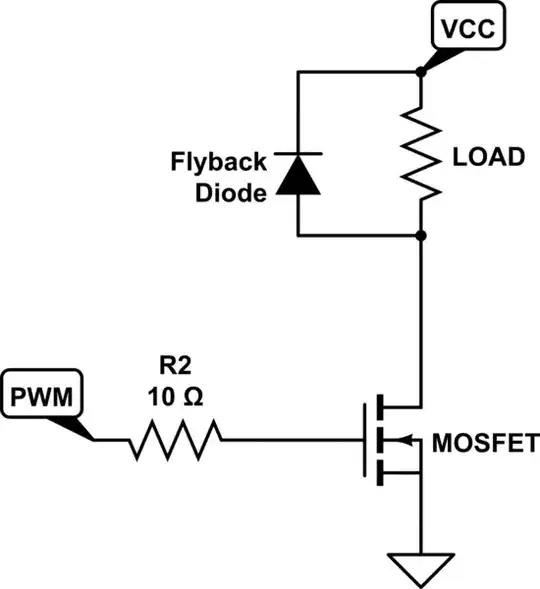

Half Bridge motor like CMOS but can be both Nch with PWM boost cap for side boost for Vgs but RdsOn can be ohms to mohms. You generally choose FETs 5x to 10x desired current to make cooling them easier.

Plan B

Transmission lines , traces and twisted pairs are also 2nd order systems with \$\sqrt{L/C} \$ ratios, so its best to match the source impedance to the path.

here for a very short path but a load capacitance.

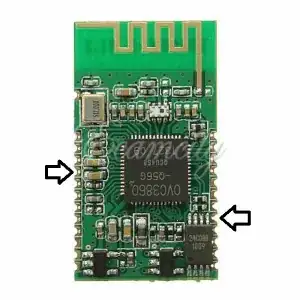

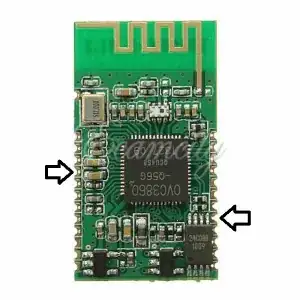

What can you measure & learn from this photo?

TL:DR

Mods ;) feel free to edit

In transformer currents, ringing is a sure sign of 5th order effects from saturation current or over-voltage.

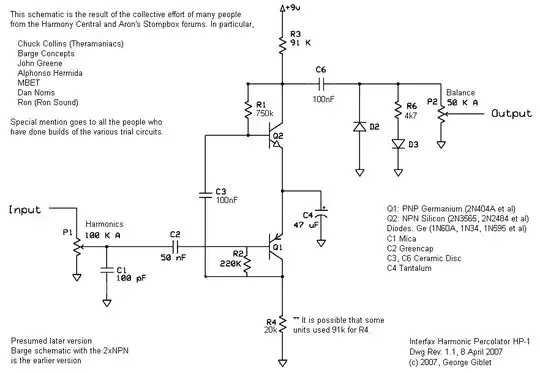

More harmonics

My Law of Harmonics are expanded:

EVEN harmonics are caused by any amplifier as tubes, FETs and BJT's are quadratic devices.

Yet perfect symmetry of square waves cancel all even harmonics.

Duty cycle errors from 50.0% can be easily measured on a Spectrum Analyzer by correlation with 2nd harmonic distortion..

Vbe & Vgs control the output current with 2nd order curves unless there is feedback to reduce the modulation. ( degeneration and negative feedback )

Clipping can generate all harmonics (unless perfectly symmetrical which is rare)

In complementary logic devices duty cycle of logic can be easily and precisely measured by the 2nd harmonic ratio on a spectrum analyzer.

Pulse asymmetry is due to the imbalance of RdsOn or unequal prop delays in an XOR.

So the extreme case of a narrow pulse has all harmonics up to the 1st missing harmonic equal to the resonant frequency of a parasitic LC circuit or the gap wavelength of a repetitive arc in MHz triggered by Grid or RADAR rates.

Pour s'amuser

http://www.falstad.com/fourier/