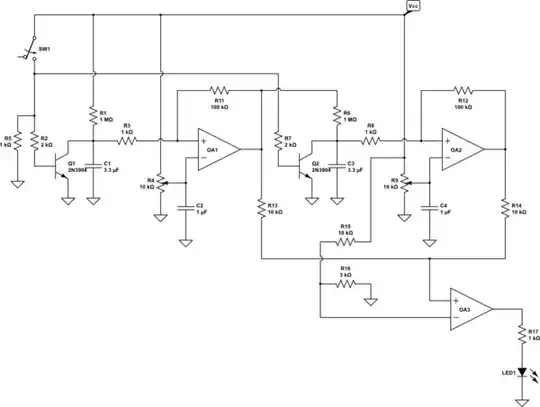

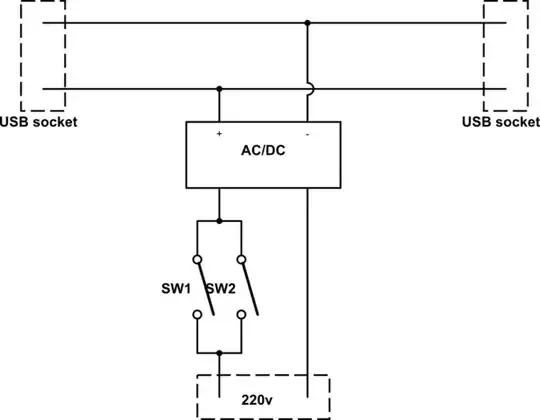

I am using an AD652 as a synchronous frequency-to-voltage converter in the layout shown below. I conducted a series of measurements of the output voltage (Vout) across a wide range of input frequencies (each of which was held constant for the duration of the measurement) and found that Vout experienced instabilities in particular regions of frequencies (each fluctuating in a periodic manner).

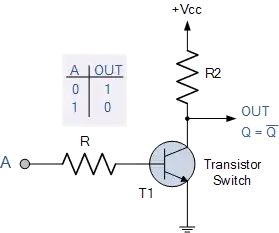

The bounds of these regions coincided with multiples of the clock frequency used (fclk = 2.5MHz), which led me to assume that the issue might have something to do with the timing in the logic circuit (AND gate, D-flop, D-latch -- on the bottom right).

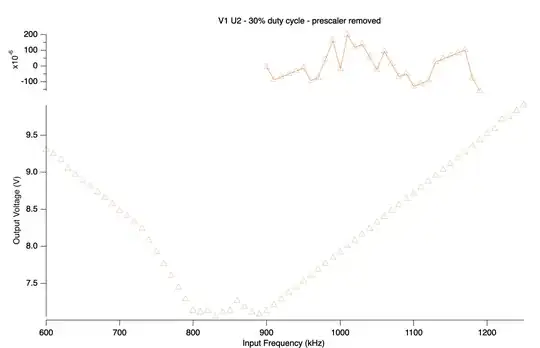

The following graph shows the residuals associated with the linearity of the positive and negative slopes, where the residuals of the negative slopes are usually 3 orders of magnitude greater than those of the positive slopes.

This is an additional graph I made, showing the relationship of the input frequencies relative to the clock frequency (25MHz):

I'd appreciate any help in understanding:

- Why the Vout - Fin graph follows this jagged relation

- Why the linearity and stability of voltages varies in a symmetric fashion

- Is there any way of mitigating the instabilities in output voltage experienced

Re. Tony Stewart:

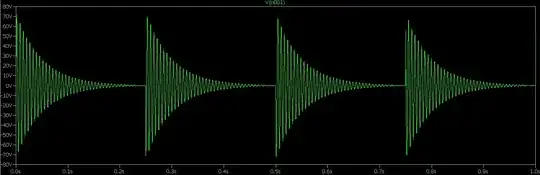

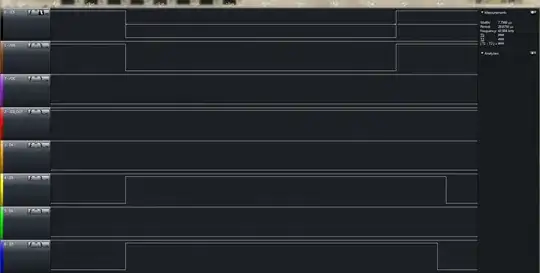

The clock signal I obtained at pin 10 is as follows:

An example of an input frequency signal supplied by a MB506 wave generator is:

An example of the periodic fluctuations in output voltage experienced, measured at an input frequency of 70MHz, displayed a repeating dip (with ~0.167s periodicity):

An example of a stable output voltage, measured at a 47MHz input frequency is:

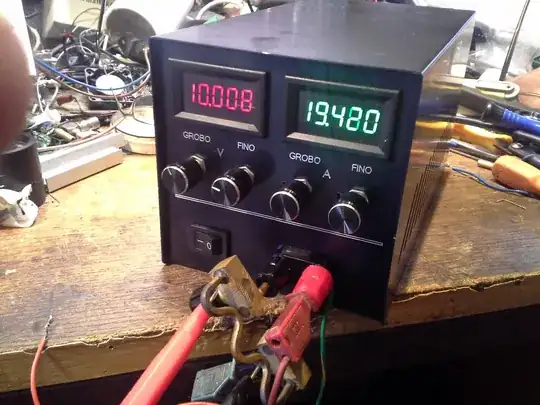

I also found that the pulse width of the input frequency is of concern since up until now I have only been investigating the output voltage for a given square wave input frequency. However, taking a closer look at the theory of a charge-balance type VFC, it seems that having a shorter duty cycle may improve the stability of the output voltage.

These are the results I obtained for a range of duty cycles:

The output voltage remains linear across the greatest input frequency range for a 50% duty cycle. I measured the smallest residuals in linearity for the 20% duty cycle, but this was over a restricted range for both frequency and voltage.