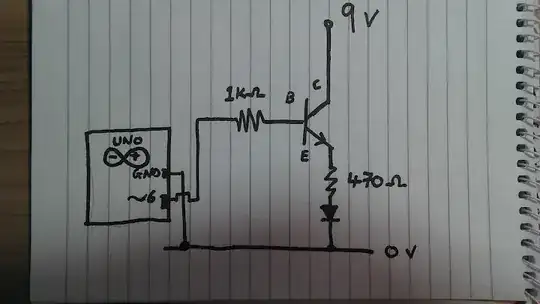

The way to see what the actual gain is, is to embrace something LvW absolutely got correct -- that there is no negative feedback to worry about. That's because the base is being directly driven by an ideal source. The next thing to realize is that your effective collector resistance is the parallel of base-collector resistance (I'll call it \$R_{_\text{B}}\$) and the positive supply-collector resistance (I'll call it \$R_{_\text{C}}\$), or \$5\:\text{k}\Omega\$. The reason that this is true is that the base end of \$R_{_\text{B}}\$ is driven by an ideal supply and the high end of \$R_{_\text{C}}\$ is driven by \$V_{_\text{CC}}\$. So the collector "sees" two resistors in parallel.

At this point, it really is \$A_V\approx -\frac{R_{_\text{C}}\,\mid\mid\,R_{_\text{B}}}{R_{_\text{E}}+r_e^{\:'}}\$.

By using a large enough \$V_{_\text{CC}}\$ you can get an acceptable DC bias. It's just that it would need to be higher than often expected. The DC bias could definitely be improved.

Let's look at what they claim. They assert that \$r_e^{\:'}=20\:\Omega\$. This implies that \$I_{_\text{E}}=1.3\:\text{mA}\$ (give or take a little depending on what you take as the device temperature.) This means that the BJT terminal voltages are: \$V_{_\text{E}}=1\:\text{k}\Omega\cdot 1.3\:\text{mA}=1.3\:\text{V}\$, \$V_{_\text{C}}=V_{_\text{CC}}-10\:\text{k}\Omega\cdot \left(1.3\:\text{mA}\frac{\beta}{\beta+1}\right)\$, and \$V_{_\text{B}}=V_{_\text{C}}-10\:\text{k}\Omega\cdot \left(1.3\:\text{mA}\frac{1}{\beta+1}\right)\$. Given that for active operation it must be that \$V_{_\text{C}}-V_{_\text{E}}\ge 1\:\text{V}\$ (the \$1\:\text{V}\$ comes from an estimated base emitter voltage of \$700\:\text{mV}\$ plus another \$130\:\text{mV}\$ needed across \$R_{_\text{B}}\$ to supply the base current plus some allowance for output signal excursions, etc. -- it really should be much more than that, in practice) you can work out that in your case \$V_{_\text{CC}}\ge15.13\:\text{V}\$. So it can be DC biased. But with caveats. If you wanted any room for output signal, you'd need more.