I have some data and would need some help to design a schematic. My target is to deal with the inrush current. I have a supply voltage range of 25-42V. A capacitive load of 1500uf. So I would like to charge this capacitor with a max 1A current in less than 200ms. For this, my idea is to use a PMOS and operate it in a linear region only. Gate of FET should be controlled in such a manner that max 1A drain current can flow. Maybe a PWM signal should be given to the gate or something else? I am looking for a rough schematic so that I can proceed it further. Thanks.

-

Up to what voltage should the capacitor be charged to? – Sim Son Mar 03 '22 at 20:00

-

What if you were to ramp the gate voltage such the output of the FET ramps from 0 V to (25 V to 42 V) over 20 ms? – SteveSh Mar 03 '22 at 20:04

-

@SimSon around supply voltage. – sikhar Mar 03 '22 at 20:21

-

@SteveSh i didn't get. can you explain it more. – sikhar Mar 03 '22 at 20:21

-

2Does this answer your question? [Capacitor charging with a MOSFET](https://electronics.stackexchange.com/questions/610604/capacitor-charging-with-a-mosfet) – hacktastical Mar 03 '22 at 22:44

-

_"I would like to charge this capacitor with a **max** 1A current"_ - why? – Bruce Abbott Mar 04 '22 at 03:31

-

@BruceAbbott this is the requirement. 1A current will flow for 200ms and will charge the capacitor upto supply voltage level (25 to 40V) – sikhar Mar 04 '22 at 08:55

-

_"and will charge the capacitor upto supply voltage level (25 to 40V)"_ - so it's only 40V now? What is the maximum current the load will draw in operation, and how much voltage drop is acceptable after the capacitor is charged? – Bruce Abbott Mar 04 '22 at 20:02

-

@BruceAbbott 25 to 40V is the range of supply voltage. Whatever voltage we will give, capacitor will charge up to that level. The capacitive load can draw less then 1A. "how much voltage drop is acceptable after the capacitor is charged", at which point you are talking about voltage drop. – sikhar Mar 04 '22 at 20:18

-

I see what you are saying now. The capacitor _is_ the load. So, how close to the supply voltage must the capacitor voltage get in 200ms? – Bruce Abbott Mar 04 '22 at 20:21

-

does it depends on how close we place the supply? – sikhar Mar 04 '22 at 20:28

2 Answers

What you are describing is basically a constant current driver. Instead of designing your own constant current source you could use a (LED) driver that does both high-side current monitoring and high-side switching. Note that the capacitor will be charged to supply voltage, so it needs an appropriate rating.

- 2,673

- 11

- 26

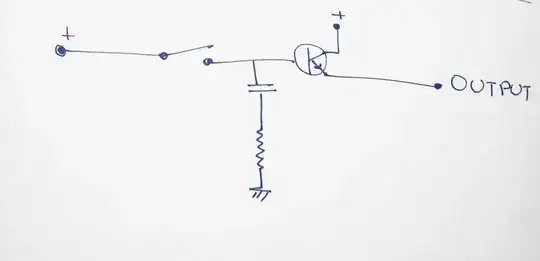

M1 (a PMOSfet) should be large enough to take about 1A, and dissipate some heat for a fraction of a second. Usually, M1's drain also feeds current to a resistive load attached across C1 - this current will slow C1's charging. The voltage drop across R3 (current-sense resistor) might also be of concern, but was not part of the "spec". The 2-ohm value limits charging current to 0.35A...a smaller value increases charging current proportionally. For example, a 0.82 ohm resistor should limit charging current to 1A.

R2, R4 are needed to keep gate voltage within acceptable limits (usually around 10V). Q1 is any small NPN transistor that can take 40V Vce.

- 23,591

- 1

- 22

- 50

-

-

1No, R3 is critical to this current regulator. There's up to one diode-drop across it (0.7v). – glen_geek Mar 04 '22 at 12:36

-

can you explain about D1 and D2. What I am thinking to turn on the Q1. is it right? – sikhar Mar 04 '22 at 18:46

-

D1, D2 provide a ~1.3V DC reference voltage for Q1's base-to-GND. You *could* substitute a 1.2V shunt-type voltage reference, but it would be over-kill. When charging current causes a voltage drop across R3 greater than roughly half of this 1.2V, Q1 conducts less, which throttles-back M1. When C1 is fully charged, Q1 turns on hard, which also turns M1 on hard. – glen_geek Mar 04 '22 at 22:21

-

What if i use NMOS in this case? and the rest working is same. Just M1 would be NMOS. will that work...or do i need a gate driver circuit for NMOS. – sikhar Mar 09 '22 at 12:38

-

No, NMOS control is a major change, requiring too many changes - a different circuit. – glen_geek Mar 09 '22 at 13:49

-

I think to control the gate of NMOS, we need a circuit like charge pump, so I have that in my system. That i can use. Now how to hold the NMOS in linear region to charge the capacitor? could you give some hint? So that i can try. – sikhar Mar 09 '22 at 15:36

-