I need to (extremely) reliably detect the status of a normally-closed DPST momentary switch at the end of a short distance of cable (max. 3m, 22 AWG).

I propose to do this with two entirely independent circuits, driven with arbitrary pulse-trains generated by an MCU. Each circuit will have a dedicated LDO to supply a higher signaling voltage (5V), which will be modulated by a MOSFET attached to the MCU. This should allow the MCU to detect mis-wiring, short to ground, short to any supply rail, short to a supply rail at a voltage higher/lower than the intended voltage, etc.

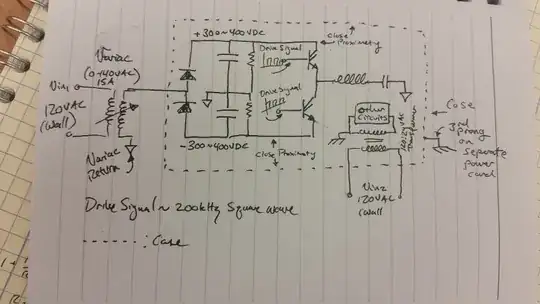

This is the high-level block diagram (apologies for the quality – too much coffee this morning):

EDIT: These should clearly be P-channel MOSFETs as high-side switches, not N-channel. Mis-drew them. Excellent catch by @brhans.

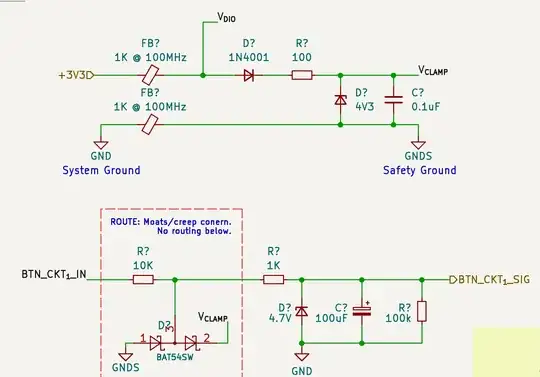

And this is the proposed input conditioning circuit (also drafted quickly for the purposes of feedback – please let me know if you spot any mistakes!):

My objective is that this input conditioning circuit will protect the MCU against ESD or more prolonged unintentional shorts to supply rails. The MCU will implement low-pass filtering, etc. and read these inputs with an ADC peripheral.

Overall, my questions are as follow:

- Is the overall concept (in particular, use of the separate LDOs) reasonable?

- Any feedback on the implementation of the input conditioning circuit?

Thank you for the advice and help! Really appreciate the StackExchange community.

EDIT I don't have a lot of details on the environment – it may be assumed to be a reasonably harsh electrical environment, in proximity to (smaller) brushless motors and other industrial equipment.