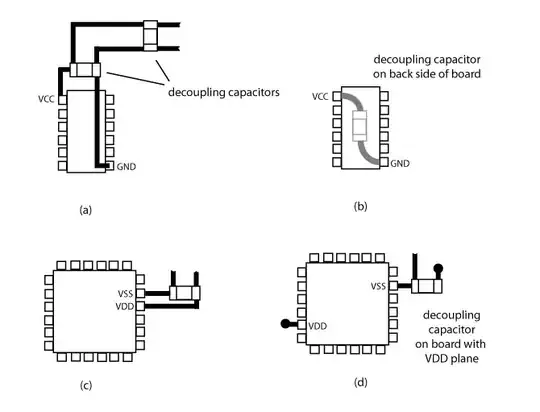

See this image which gives four options to place decoupling capacitors:

(from http://www.learnemc.com/tutorials/Decoupling/decoupling01.html)

I would say option (d) isn't good - I would recommend someone to place the capacitor near VDD instead of VSS. Is this right? The same goes for (c).

Generally: what's the best place to place a decoupling capacitor? Where would it have the most effect? And, more important, why? I'd like a theoretical explanation.