Is it reasonable to float an AC signal on top of a HV DC bias with a HV Capacitor and low input bias current OpAmp?

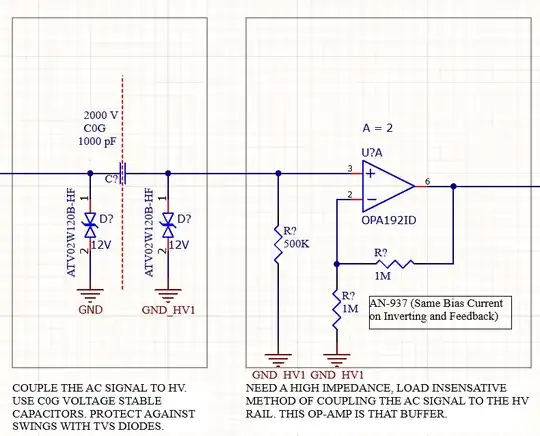

The idea is that a fixed frequency AC signal (~1V pk-pk) comes from the left, is coupled to whatever DC bias voltage GND_HV1 is on the right, and buffered by the OpAmp.

Some protection diodes prevent damage to circuitry on the left/right from rapid voltage changes in GND_HV1.

A voltage stable cap is used to prevent capacitive coupling changes based on the GND_HV1 bias.

If the design is feasible, is there any advantage to using a FET based OpAmp over a BJT one?

Most capacitively coupled designs (discrete or monolithic) discretize and encode the input signal before coupling, and decode after coupling. This introduces delays and noise on the coupled signal. I figure there's a reason I've not come across this topology before, what is it?