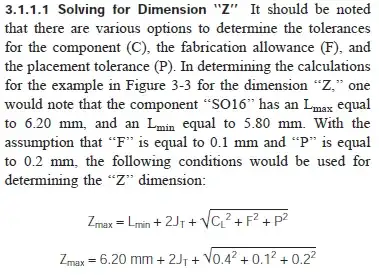

I'm trying to make a NAND SR-latch using only transistors, by combining a schematic for a NAND gate and a schematic for an SR-latch. The resulting circuit looks like this:

(One thing not shown is that the switches are pulled down. Switches are normally closed, but I open them to Set or Reset)

Set and Reset work when I open them, but it is not stable when both are closed. It always goes back to Q, even though the circuit is completely symmetrical.

I've rebuilt the circuit to make sure I match the schematic, but still get the same problem. Is there something wrong with my resistor values, perhaps? (The NAND gate design works fine when tested in isolation.)

Bonus question: Is there a good online simulator that would help me debug this issue?