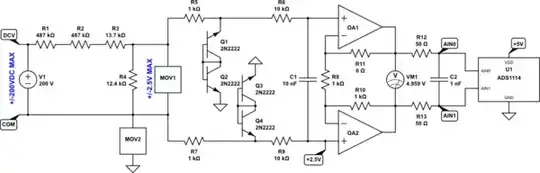

The input driving below circuit has only two states: \$-10V\$ for OFF and \$0V\$ for ON. Why can't we apply this input directly to the gate? I mean removing the resistor \$R_G\$ doesn't seem to change anything?

I understand \$R_D\$ is there to ensure the jfet is in hard saturation, operating in ohmic region.

But I don't get the role of \$R_G\$. It is not part of voltage divider bias or anything. It is simply shorted to the ground. Why can't I remove it? (Maybe removing \$R_G\$ even helps here.. as the the input impedance of jfet gate is very high, so the input signal doesn't have to provide much current.)

Source: https://archive.org/details/ElectronicPrinciples8thEdition/page/422/mode/2up?view=theater