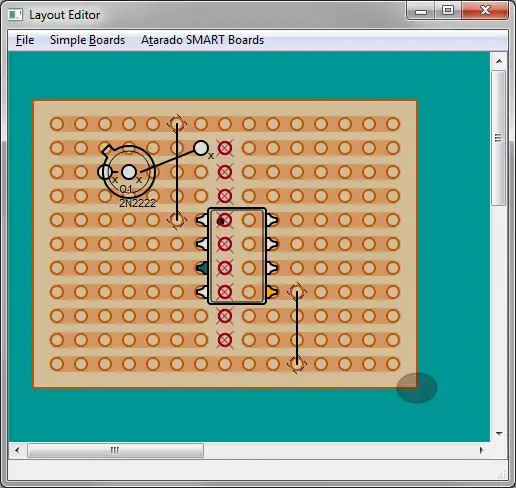

I am trying to mitigate a self turn-on behaviour in an inverter simulation. It is a 400V design using. The H bridge uses SPP20N60C3 MOSFETS. The AC frequency has been sped up to 500Hz instead of 50Hz (the problem is the same at 50 Hz) to speed up the appearance of the problem. The gate driver is an IR2110. I can provide the asc file if needed, and Infineon provides the SPICE model for the IR2110. NB: SPICE must used modified trap and solver set to alternate for the simulation to work. I used a spwm signal with a dead time control circuit using a duty cycle shortener circuit provided in this post : duty cycle shortener

The simulation shows a short current spike across all MOSFETS since they are all shorted, that happens when the complementary MOSFETS turn on. The spurious spikes on G1 and G3 gate signals are easily seen. I wonder if it is a simulation artefact, or if this would happen in real life. I tried to change gate resistance, having a 10K gate to source resistor, as most chinese driver boards application schematics include them (although IR2110 has active low drivers, so it should not be required ?)

Also, getting rid of the output LC filter does not change anything.