I have checked a few bit bang posts here but still couldn't figure it out.

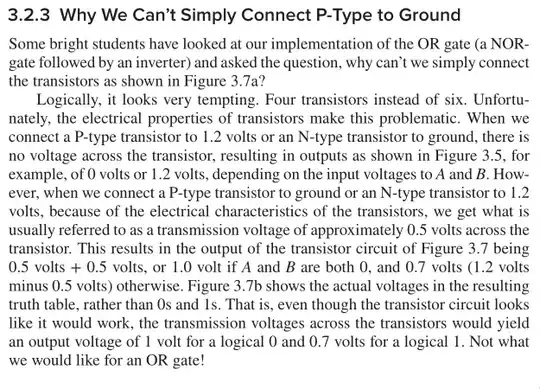

The datasheet of the EEPROM is at: Datasheet of FT93C66A

I tried to interface with SPI but to no avail, so I decided to use bit bang instead. The MCU runs at 50MHz so I also need to add some delay as some posts mentioned.

Configuration:

PA2->SCL, PA4->DO, PA5->DI, PA6->CS, VCC and GND are also linked properly. ORG is disconnected for 16-bit mode.

Initialization of PORT A

Because I use bit bang, I only setup PA0 and PA1 for UART to send debugging message to PuTTY;

PLL runs at 50MHz;

UART part code is tested as correct so I don't show it

void PortA_UART_Init(void){

// Initiate Port A for UART VCOM communication to PC using PuTTY

SYSCTL_RCGC1_R |= 0x00000001; // Activate UART 0 that interfaces PA0 and PA1

// Check page 651 of datasheet - using U1Rx and U1Tx

SYSCTL_RCGC2_R |= 0x00000001; // Activate Port A

UART0_CTL_R &= ~0x00000001; // UART0 module disable, check datasheet page 918

// ----- Initialization -----

UART0_IBRD_R = 27; // IBRD = int(50,000,000/(16*115200)) = int(27.1267)

UART0_FBRD_R = 8; // Fractional part = int(0.1267 * 64 + 0.5) = 8

UART0_LCRH_R = 0x70; // Data sheet page 916, 8-bit FIFO, One stop bit, No parity bits

UART0_CTL_R |= 0x00000001; // UART0 module enable, datasheet page 918

GPIO_PORTA_AFSEL_R |= 0x03; // Enable alternative function for PA1 and PA0 (number 2 is chosen by PCTL)

GPIO_PORTA_DEN_R |= 0x03; // Enable PA1 and PA0

GPIO_PORTA_PCTL_R =

(GPIO_PORTA_PCTL_R&0xFFFFFF00)+0x00000011; // Set alternative function 1 for PA1 and PA0

GPIO_PORTA_AMSEL_R &= ~0x03; // Disable analog on PA1 and PA0

}

- Now I also initiate PA2, 4, 5 and 6 for bit bang:

void PortA_Bit_Bang_Init(void){

// Initiate Port A for bit bang, no SSI initialization

// Majority of initialization code for PortA already done

GPIO_PORTA_DEN_R |= 0x74; // Enable PA6, PA5, PA4 and PA2, 0111_0100

GPIO_PORTA_DIR_R |= 0x64; // PA2, PA5 and PA6 for output

GPIO_PORTA_AMSEL_R &= ~0x34; // Disable analog on PA5, PA4 and PA2

}

Because PPL runs at 50MHz, while EEPROM runs around 1-2MHz, I manually added a lot of delay code using a timer. The delay works well so I don't post the code here.

My question: Is the following pseudo code correct for EWEN?

EWEN: Must be sent before any operation: Send 100 followed by 11XXXXXX (I choose 11000000) so total of 11 bits. This is also the reason I choose to use bit bang, because standard SPI uses 16 bit FIFO. The EEPROM also needs 27 bits for writing under 16-bit mode.I have no idea how to use the FIFO to do this.

Pseudo code:

CS High

Clock Low

Delay for 1ms

// Send start bit and OpCode - 100

PA5 High (PA5 connects with EEPROM's DI) - this is sending 1

Delay for 1ms

Clock High

Delay for 1ms

Clock Low

Delay for 1ms

PA5 Low - this is sending 0

Delay for 1ms

Clock High

Delay for 1ms

Clock Low

Delay for 1ms

Clock High - PA keeps low for the second 0

Delay for 1ms

Clock Low

Delay for 1ms

Delay for 1ms

// Send 1100_0000

PA5 High - Send 1

Delay for 1ms

Clock High

Delay for 1ms

Clock Low

Delay for 1ms

Clock High - PA5 keeps to be high for the second 1

Delay for 1ms

Clock Low

Delay for 1ms

PA5 Low - this is sending 0

Delay for 1ms

Clock High

Delay for 1ms

Clock Low

Delay for 1ms

Clock High - PA5 keeps low for second 0

Delay for 1ms

Clock Low

Delay for 1ms

Clock High - PA5 keeps low for third 0

Delay for 1ms

Clock Low

Delay for 1ms

Clock High - PA5 keeps low for fourth 0

Delay for 1ms

Clock Low

Delay for 1ms

Clock High - PA5 keeps low for fifth 0

Delay for 1ms

Clock Low

Delay for 1ms

Clock High - PA5 keeps low for last 0

Delay for 1ms

Clock Low

Delay for 1ms

// Pull down CS

CS Low

Delay for 1ms

CS High

```