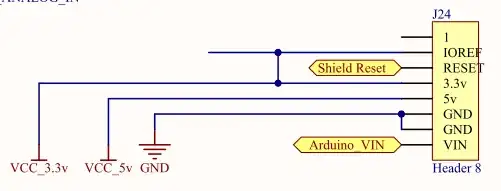

I designed a Arduino shield compatible board around the NXP LPC4337JBD144. so far I have been unable to get the first revision to program.

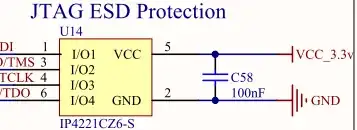

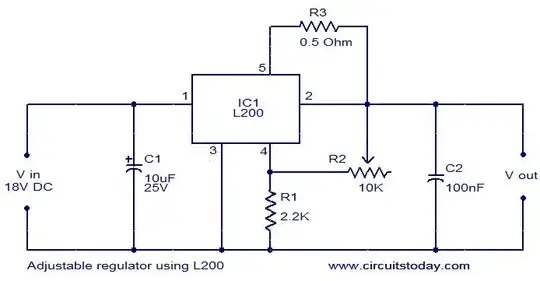

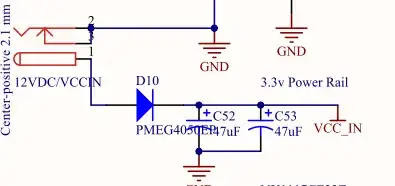

In the first design the JTAG header was not setup correctly, there were no bypass capacitors, the USB did not have all the pullups/pulldowns it needed, the DBGEN and TRST pins were not broken out to jumpers, and the Ethernet section did not follow spec as strict as it should have. I have able to add all the pullups to the JTAG and pull the DBGEN high and the TRST low by modifying the PCB with external jumper wires and resisters. I am still unable to program it with my JTAG.

I should note that the rev one PCB is only populated with what is necessary to get the chip programming and running, no additional hardware passive or active. I have tested that I am getting the correct signals from the JTAG and they are going to the right pins. I checked the crystal as well but I don't get a signal because the crystal will no initialize until the chip is programmed because the first thing that runs in a system configuration routine that sets up all PLLs and external oscillator settings. Everything on the first revision PCB has been check thoroughly with an oscilloscope, JTAG signals, crystals, and power section.

That being said I have been battling with this first revision for several weeks, I have tried everthing that NXP support has recommended, I have reviewed the schematics for several evaluation boards from NXP, Keil, and Hitex modifying my PCB along the way to bring it up to the ARM standard spec to no avail.

At this point I am convinced that the design is flawed in too many ways putting it way out of the standard specifications for an ARM Cortex M4 that it cannot be fixed with external modification to the PCB and that second revision of the design needs to be tested. This is a very time sensitive design, I was hoping to at least get the first one working then have the second revision be a fine tuning process. That being said I need to get a new design out to the fab house to keep my professors happy. I'm looking for constructive feedback on my new design, I have spent about two weeks looking through this design on my own and with the help of others in attempts to find anything that could be a serious potential problem down the road. I have been double checking the reference schematics and datasheet and I personally haven't detected any problems so far (most of my previous design work has been with AVRs).

EDIT: My board is 4 layers, the two outer layers are for signals and the two inner layers are a ground plane and a power plane. Right now I have the negative space on the two outersignals filled in with a ground fill polygon, could that cause some problems with the board such as ground loops?

Below I have attached the smart PDF for my Altium Project it includes the schematic and PCB design. https://www.dropbox.com/s/qb9ptr67v6msmh0/Abstract%20Hardware%20Device.pdf

Altium PCBdoc: https://www.dropbox.com/s/s7s0aw3yuh4va3g/Abstract%20Hardware%20Device%20PCB.PcbDoc

EDIT2: share link updated to Dropbox one. Altium PCBdoc shared.

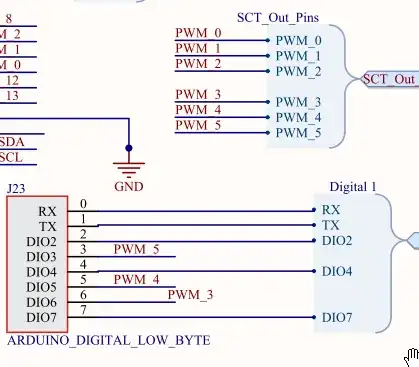

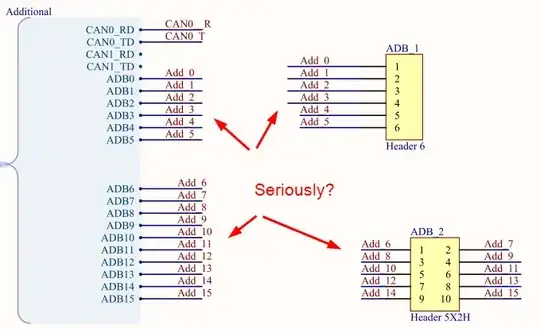

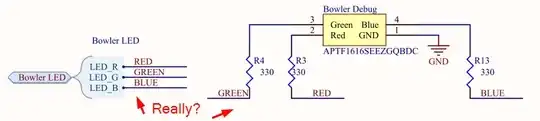

As a rule, net-labels make schematics harder to read and maintain. There are a few, specialized situations where they are beneficial, and if you don't know what those situations are, you don't have one. This is not one of them.

As a rule, net-labels make schematics harder to read and maintain. There are a few, specialized situations where they are beneficial, and if you don't know what those situations are, you don't have one. This is not one of them.