I am testing a QSPI NOR FLASH device on a board I designed. It's datasheet is here.

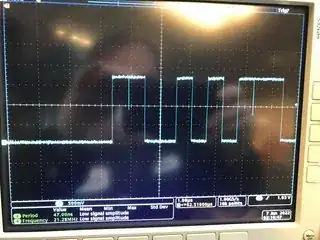

Although it is working, I am seeing some glitches on the FLASH SDO (Serial Data Output) line. All other signals are inputs and look fine. I believe it is working because the glitch goes away before the clock edge.

It looks like the glitch is happening on a transition boundary, when the signal could switch from 1 to 0 or from 0 to 1 but won't.

I have attached a photo showing this. Any idea on what could be causing this?