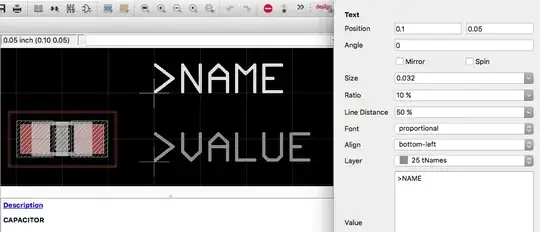

I am trying to play around a 6T SRAM cell by simulating it's write operation in Cadence Virtuoso. The NMOS and PMOS specifications are 120/45 nm and 310/45 nm. The Bit select is kept at constant 1 and I want to write 0 and 1 in cell after 10n interval Here is the schematic view of it:

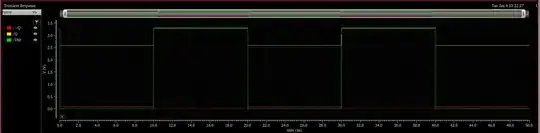

Now, When I give 1 at Vbit, the cell is written with 1 as expected. But while pulling down the Q node, the cell values get corrupted and some intermediate value is stored in cell. In my knowledge, two inverters connected in feedback loop will have two points of stable equilibrium and one point of unstable equilibrium, but here the stable states of Q and Q` are in none of them., something like :

Can anyone please explain why this happens? Does this have anything to do with unconnected Qbar input of cell?

Also, please note that the above observations are made at VDD=3.3V. This is very confusing, can anyone please elaborate ?

Thanks