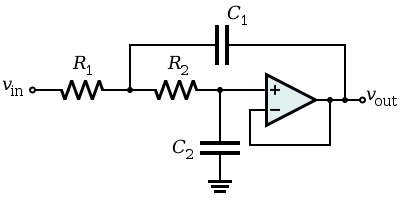

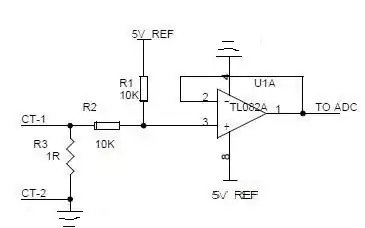

So here's the circuit and output voltage, the model is AD620:

So according to theory (Vout = 49400/49400 +1)*(2-1) ) i should obtain 2V as the output voltage.

Well what i got in LTSpice was a value around 2V with a lot of spikes, why does that happen? Also it doesn't hit the 2 V immediately. In the very beggining it appears to have some sort of transition.

Also from what i understood the reference voltage (taken from here https://www.analog.com/media/en/technical-documentation/data-sheets/AD620.pdf) is that it pretty much just defines the zero output voltage. What would happen if i change it to half of the value of the power supply?